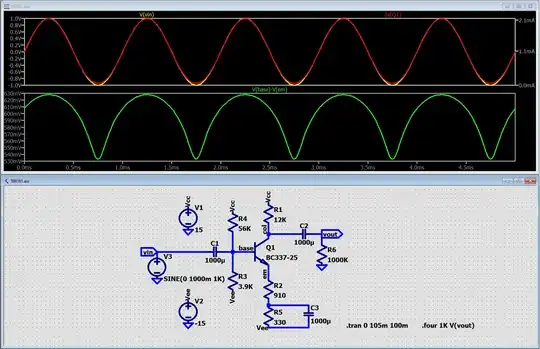

Schematic

simulate this circuit – Schematic created using CircuitLab

Sanity Checks

Your output swing is \$\pm 12\:\text{V}\$ or \$24\:\text{V}_\text{PP}\$. Your power supply rails are \$\pm 15\:\text{V}\$ or \$30\:\text{V}\$. In addition, your emitter has to swing with the input, so that's \$\pm 1\:\text{V}\$ or \$2\:\text{V}_\text{PP}\$. Finally, \$Q_1\$ cannot be allowed to saturate. So there is a minimum collector-emitter voltage that must be reserved out. Not less than \$1\:\text{V}\$, as you don't know what the base-emitter voltage may be here.

So, accounting for all of the above, there's only \$3\:\text{V}\$ left over to work with. And that has to be used for the following items:

- You really do not want the collector current to go to zero. You can't drive the collector right up to the plus rail. So you absolutely must allow some voltage margin for the collector resistor.

- You really do want some voltage margin for \$R_{_{\text{E}_2}}\$ as this sets the quiescent current.

- The voltage across \$R_{_{\text{E}_1}}\$ cannot fall to zero (see #1 above) and will be about \$\frac1{\mid A_v\mid}\$ of whatever margin you reserve for #1, above. Or, put another way, #1 will be about \$\mid A_v\mid\$ times whatever you reserve here.

I think you can see why things are tight.

But looking at this, I'd say it is doable. If I set aside about \$500\:\text{mV}\$ for #2, then this means about \$200\:\text{mV}\$ minimum across \$R_{_{\text{E}_1}}\$. Sure, the \$2\:\text{V}_\text{PP}\$ rides on top of this and that means that there will be quite a %-variation of collector current and therefore some variation of voltage gain due to changes in \$r_e^{\,'}\$ (which is also affected by temperature.) But it is livable.

So it passes the basic sanity check.

That said, I'd like to see \$C_{_\text{E}}\$ set very large, so as to keep variations of the voltage across \$R_{_{\text{E}_2}}\$ from causing trouble, given how tight things are. A few millivolts of variation are tolerable here. But things are very tight. So getting sloppy is a recipe for trouble. Making \$C_{_\text{E}}\$ large mitigates this worry of mine.

Design

I'm going to set off \$500\:\text{mV}\$ for \$R_{_{\text{E}_2}}\$, so there's only \$2.5\:\text{V}\$ left now for \$R_{_\text{C}}\$'s minimum voltage margin plus the minimum voltage margin for \$R_{_{\text{E}_1}}\$. Since those are related to each other by the voltage gain, \$A_v\$, it's all in a single package. Without accounting for \$r_e^{\,'}\$ in this mess, this means \$\frac{2.5\:\text{V}}{\mid A_v\mid +1}\approx 190\:\text{mV}\$ for \$R_{_{\text{E}_1}}\$'s minimum and about \$2.31\:\text{V}\$ for \$R_{_{\text{C}}}\$'s minimum.

From this, I find:

$$\begin{align*}

V_{_{\text{C}_\text{Q}}}&=+15\:\text{V}-2.31\:\text{V}-12\:\text{V}&=690\:\text{mV}

\\\\

V_{_{\text{E}_\text{Q}}}&=-15\:\text{V}+500\:\text{mV}+190\:\text{mV}+1\:\text{V}&=-13.31\:\text{V}

\end{align*}$$

There's no quiescent current specification, no THD specification, no temperature stability specification, etc... so I can pretty much pick any quiescent current I want.

Standard values for resistors may be a problem if you are supposed to nail the voltage gain, exactly. But I suspect that's not a problem. (It better not be, because BJTs vary a lot, temperature varies, and this stage is going to have a varying voltage gain anyway because of the very wide swings and practically no voltage margins to work with.) So we can get close to the right voltage gain and just be happy.

So let's just pick \$R_{_{\text{C}}}=4.7\:\text{k}\Omega\$ as a starting point. (Have to start somewhere.) Since we need to drop a quiescent \$2.31\:\text{V}+12\:\text{V}=14.31\:\text{V}\$, we find \$I_{_{\text{C}_\text{Q}}}=\frac{14.31\:\text{V}}{4.7\:\text{k}\Omega}\approx 3\:\text{mA}\$.

I don't know what the BJT \$\beta\$ is (the emitter current will be slightly more), but we can estimate \$R_{_{\text{E}_1}}=\frac{190\:\text{mV}+1\:\text{V}}{3\:\text{mA}}\approx 390\:\Omega\$. Convenient.

And now \$R_{_{\text{E}_2}}=\frac{500\:\text{mV}}{3\:\text{mA}}\approx 165\:\Omega\$. We need to pick something standard. Either way, this will mess with the reserved \$500\:\text{mV}\$. But that's okay. Because things are so tight, let's use a smaller resistor value here, \$R_{_{\text{E}_2}}=150\:\Omega\$, and recalculate that we'll drop about \$450\:\text{mV}\$, plus a little because the emitter current is a little higher. Call it \$460\:\text{mV}\$.

Guessing about \$700\:\text{mV}\$ for the base-emitter voltage, this means the base voltage for \$Q_1\$ is \$-15\:\text{V}+460\:\text{mV}+1.19\:\text{V}+700\:\text{mV}=-12.65\:\text{V}\$.

A stiff divider will have about 10% of the collector current, or \$300\:\mu\text{A}\$, in \$R_{_{\text{B}_2}}\$. So \$R_{_{\text{B}_2}}=\frac{-12.65\:\text{V}-\left(-15\:\text{V}\right)}{300\:\mu\text{A}}\approx 7.83\:\text{k}\Omega\$. Since you have a low-impedance signal generator driving this, I'm going to round the resistor value down to \$R_{_{\text{B}_2}}=7.5\:\text{k}\Omega\$ and re-calculate \$\frac{-12.65\:\text{V}-\left(-15\:\text{V}\right)}{7.5\:\text{k}\Omega}\approx 313\:\mu\text{A}\$ as the current.

Since the base current will be no worse than \$\frac1{100}\$th of the collector current, the required current for \$R_{_{\text{B}_1}}\$ is \$313\:\mu\text{A}+30\:\mu\text{A}=343\:\mu\text{A}\$. So \$R_{_{\text{B}_1}}=\frac{15\:\text{V}-\left(-12.65\:\text{V}\right)}{343\:\mu\text{A}}\approx 80.6\:\text{k}\Omega\$. Also not a standard value. Since we know the base current might be (probably is) less than estimated, we can raise the value so that \$R_{_{\text{B}_1}}=82\:\text{k}\Omega\$.

The final circuit is:

simulate this circuit

Now, I honestly have no idea if I've made some gross mistake above, except to try it out in LTspice. Hopefully, it either will confirm my hopes or else it will help me find a mistake in my above work product.

Also, all of the above adjustments to find standard resistor values have also changed some of my earlier assumptions. And it is tight in here. Real tight. There's not a lot of wiggle room for adjustments. So even if I got things right, when you build this thing I'd still expect the need for some minor, final tweaks to deal with vagaries of BJTs and resistor tolerances and the ambient temperature. There just is NOT enough headroom in order to make a design that is bullet-proof against temperature and part variations. Can't be done with so little headroom.

My last caveat is that I expect the voltage gain to be a little below expectations because I didn't account for \$r_e^{\,'}\$, which is about \$9\:\Omega\$. If you find that the gain isn't to your liking, feel free to lower the value of \$R_{_{\text{E}_1}}\$ by about that much.

Let's see.

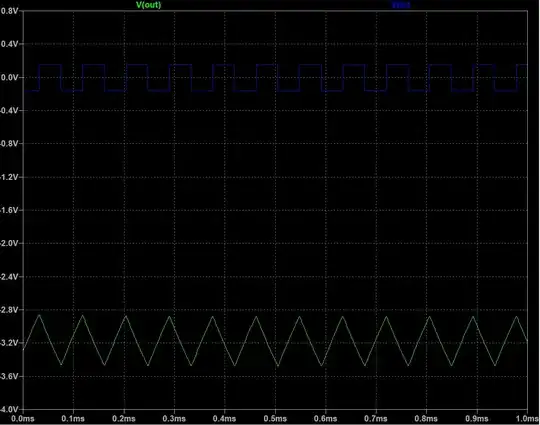

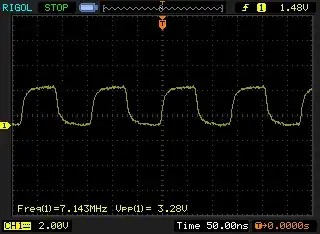

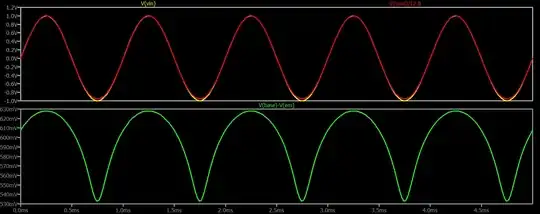

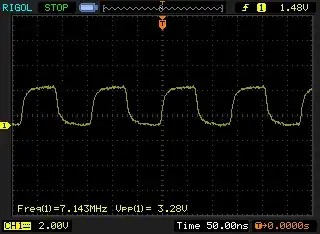

Looks like \$\mid A_v\!\mid\, \approx 11\$. Close. Plus, it worked without exhibiting any clipping. And it did this without me making any gross mistakes, either. Kind of "just worked."

You can set the emitter capacitor back to a smaller value, if you want. That will allow a larger swing there. But the ripple was only a couple of millivolts (I checked) with that large capacitor I used. Putting it back to your value will mean maybe \$80\:\text{mV}\$ of peak to peak ripple. But I don't think anyone will care that much about the consequences of it. The output will still look okay on a scope.

When you get to building one of these, just get things up and see what you have. Check the collector voltage signal, directly. If it is clipping on the bottom then you are saturating the BJT (pushing up against the emitter too tightly) and you can open things up a bit by increasing the value of \$R_{_{\text{E}_2}}\$ (because that will lower the quiescent current.) If things are clipping on the top, then do the opposite. You can use this resistor to move your collector curve up or down, that way. (Please note that I'm not talking about the output across the \$100\:\text{k}\Omega\$ load resistor. I'm actually talking about the signal variations at the collector of \$Q_1\$. Keep that straight!)