I would like to avoid using DC-DC converters for each power MOSFET in a switch-mode power supply as they are pricey, bulky, and have an input to output capacitance which can lead to common-mode noise generation.

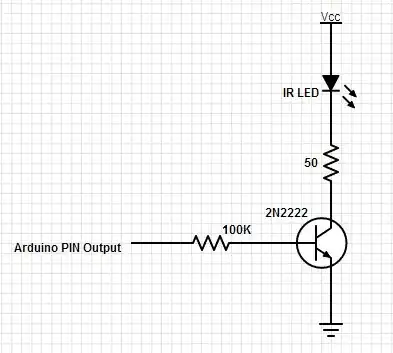

The schematic I have in mind is the following:

As the MOSFFET source will go high from time to time there will be enough energy to charge the capacitor which will power up the gate driver.

The MOSFETs are SiC if it is an important circumstance.

My questions are:

- Is there anything I should be aware of in case of using this method of making power for a gate driver?

- Is there a better schematic for this?

UPDATE: I have put 1M resistor in parallel with the capacitor and lowered the gate resistor to make the Zener current higher as Michael suggested.