I am working on a design with a Cyclone-V FPGA.

- I have a PLL that generates 4 clocks of equal frequency but with 90 degree phase shift from eachother.

- 4 DFFs running on each of these respective clocks. The outputs of these 4 DFFs are connected to a 4:1 mux.

- I would like the outputs of the 4 DFFs going into the mux to have equal path delay (or equivalently path delay to the output of the mux).

- The output of this mux is a clock connected to a global clock buffer.

- The mux selects only switch when all 4 mux inputs are low and will be low for a long time. Therefore, we are not concerned with constraining the mux select path.

- All of the circuitry is internal to the FPGA (no I/O)

The clocks are defined here:

create_clock -name {CLK_250_IN_g[0]} -period 4.000 -waveform { 0.000 2.000 } [get_pins { inst_pllgclkbuff4_cve_CLK_250_IN|inst_cycloneve_clkctrl[0].inst_cyclonev_clkena0|outclk }]

create_clock -name {CLK_250_IN_g[1]} -period 4.000 -waveform { 1.000 3.000 } [get_pins { inst_pllgclkbuff4_cve_CLK_250_IN|inst_cycloneve_clkctrl[1].inst_cyclonev_clkena0|outclk }]

create_clock -name {CLK_250_IN_g[2]} -period 4.000 -waveform { 2.000 4.000 } [get_pins { inst_pllgclkbuff4_cve_CLK_250_IN|inst_cycloneve_clkctrl[2].inst_cyclonev_clkena0|outclk }]

create_clock -name {CLK_250_IN_g[3]} -period 4.000 -waveform { 3.000 5.000 } [get_pins { inst_pllgclkbuff4_cve_CLK_250_IN|inst_cycloneve_clkctrl[3].inst_cyclonev_clkena0|outclk }]

I attempted to achieve this by constraining this path with set_max_delay and set_min_delay in my sdc (there are 4 copies of these constraints for each of the 4 registers).

set_max_delay -from [get_cells {inst_clkgen_a|inst_clkgen_phases|CLKOUT_phases[0]}] -to [get_cells {inst_clkgen_a|inst_mux4_1_CLK_OUT|Mux0}] 0.100

set_max_delay -from [get_cells {inst_clkgen_a|inst_clkgen_phases|CLKOUT_phases[1]}] -to [get_cells {inst_clkgen_a|inst_mux4_1_CLK_OUT|Mux0}] 0.100

set_min_delay -from [get_cells {inst_clkgen_a|inst_clkgen_phases|CLKOUT_phases[0]}] -to [get_cells {inst_clkgen_a|inst_mux4_1_CLK_OUT|Mux0}] 0.000

set_min_delay -from [get_cells {inst_clkgen_a|inst_clkgen_phases|CLKOUT_phases[1]}] -to [get_cells {inst_clkgen_a|inst_mux4_1_CLK_OUT|Mux0}] 0.000

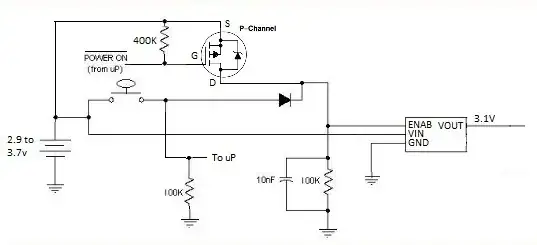

This is making no difference to the path delay from the Q output to mux.out. The resulting path delays are shown in the circuit diagram, indicating the min/max constraints are not working.

How is possible to accomplish this?