Project Description: A mini-calculator that performs addition, subtraction, and multiplication on two 4-bit inputs (0-9) and displays the inputs and resulting numbers in 7 segment displays. Aside from the two 4-bit inputs, there is also a 2-bit input to decide which arithmetic operation is used. 00 is off, 01 is addition, 10 is subtraction, and 11 is multiplication. I am only allowed to use AND, OR, XNOR, NOR, and NOT gates. Absolutely no other gates or IC's. I am to implement the project on a breadboard.

This is my current design (I adapted the binary to BCD circuit from the design of Jonk ), already tested the whole circuit and it works perfectly.

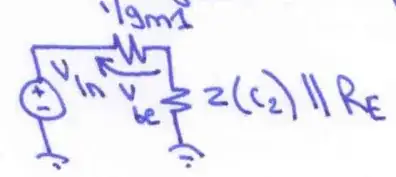

Adder/Subtractor - Uses the standard full adder circuit. I attached it into a 2's complement circuit which basically inverts the input and adds 1 to it. This is for the negative difference during subtraction, which also turns on the left bottom 7 segment's g, displaying - sign.

Multiplier - Again, using the standard full adder design. The maximum output is 81 (9x9), a 7-bit binary number.

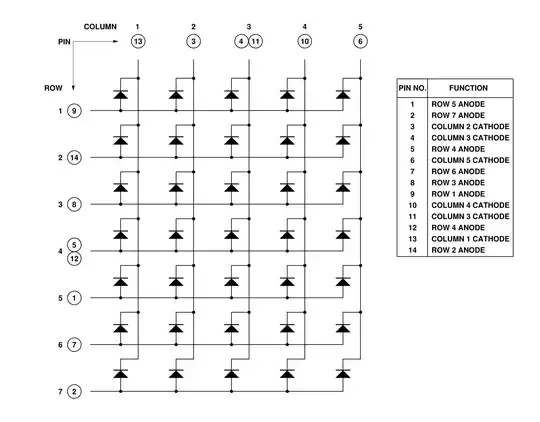

The miscellaneous gates between the adder/subtractor and multiplier ensures that only the result of the correct circuit on the corresponding 2-bit input will be passed on to the binary to BCD converter. Others in the middle of the circuit is a combinational circuit that drives 3x3 LEDs to display +, -, and x, and two rows of LEDs for the equals sign. The four combinational circuits at the right are the BCD to 7 segment decoders.

The outputs of the adder/subtractor and multiplier are fed to the binary to BCD converter, since their maximum values are 18 and 81, respectively, so I need to convert these more-than-4 bits numbers into BCD to drive them into the 7 segments decoder.

The outputs are two 7 segments at the top displaying the inputs, and a 3x3 LED for the operation (e.g. 9+7). The first 7 segment at the bottom is for the negative sign, and the second and third bottom 7 segments are for the resulting number.

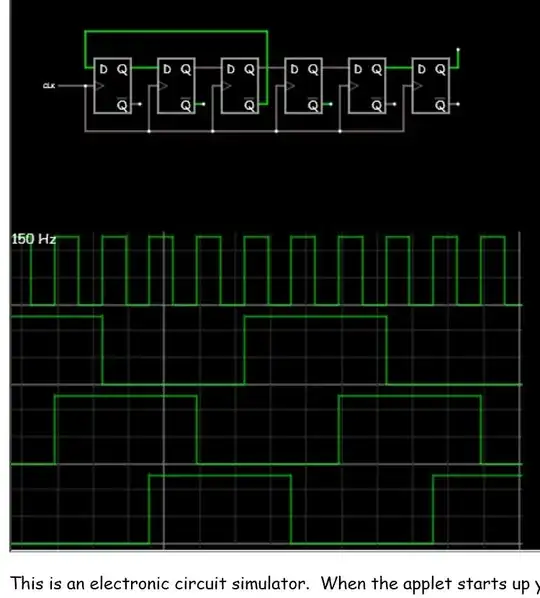

However, as seen from the picture, it uses too much logic gates. I calculated and estimated it to require more than 90 ICs, and probably around 18 long breadboards, which will be a nightmare to wire.

Is there any other way to simplify the circuit? Or any other circuit that can replace one of the blocks in the whole circuit? I'm aiming for 60+ ICs, preferably 50+. I do think that I could find a way to design a simpler binary to BCD, but the only ways I could find were the double dabble algorithm and converting binary to decimal then to BCD.