I'm working on an eighteen-layer board right now. Almost all of the signal layers have high-speed, single-ended traces that should run up to 15 gbit/s. The vias for these high-speed traces will be backdrilled to be a total length of 23 mil, keeping the via stubs no longer than roughly 1/20th of a wavelength. However, to keep costs down, there are only two drill pairs, meaning that a high-speed signal may only need to travel 3 mil down a 23 mil via. In this worst-vase scenario, the via would have a 20 mil stub, which my calculations indicate is less than 1/20th of a wavelength. This will minimize reflection caused by the stub.

However, I am unsure how to calculate the via impedance of stub. According to the Saturn PCB Toolkit, via height will non-negligibly affect impedance at such high frequencies, but this can easily be adjusted by changing the anti-pad diameter. But should my calculations account for the length of the via that the signal would actually travel (3 mil), or should the calculations still account for the entire 23 mil of via height?

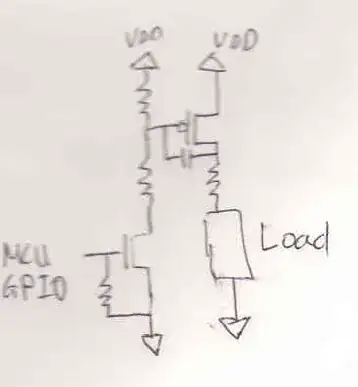

Calculating antipad based on via signal length:

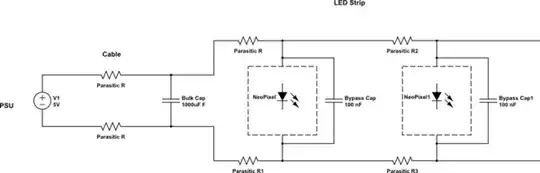

Calculating antipad based on total via height: