You know linear \$dV/dt = Ic/C \$ when large signals are current limited such as Op Amps .

And 10% to 90% step \$dV/dt = 0.35 / f_{-3dB~ BW}\$

And \$GBW = Av * BW_{-3dB} \$

You have encountered a problem with SR=0.5V/us. That is equivalent to a BW of 0.35 / 0.5 V/us = 700 kHz.

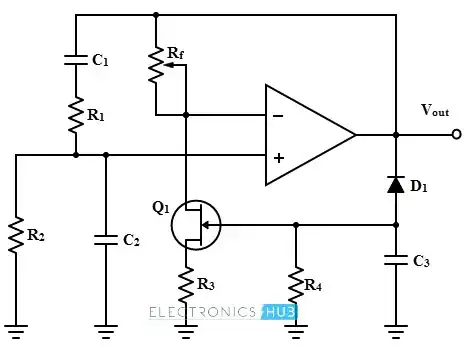

~ The Falstad web sim. is fast in simulation, but only models the Vbe vs Ic with an hFE variable and not the Miller Capacitance. When you go through inverting amplifier stages, the phase shift adds up. When you have higher than a 2nd order slope at unity gain, the way to make it unity gain stable is to add a 1st order integrator inside the loop to make it a 1st order loop at unity gain.

This 30 pF does that. However removing the default 30 pF would eliminate the slew rate in Falstad's, but 1pF (DOES NOT. Try 1 fF, not 0) as the current is low in the path of this capacitor, thus equivalent to a high impedance or RC time constant.

~ LTSpice, which simulates far slower but uses a more complex model for each capacitor. This makes little difference, if you compensate it as such ( with a bigger one than all the rest combined from each stage) but will, if you remove the cap in this > OP Amp> Internals model simulation.

~ Also remember that Falstad's will use an Ideal Op Amp with zero input offset,Vio and zero Zout and thus infinite current-limit and slew rate but gain limited gain (default = 1e5) for input error gain. So when necessary add 200 ohms in series with output before the negative feedback (NFB) for realism as NFB lowers the Zout by design. We would call this a Level 1 simulation and the 741 internals model a Level 2 in complexity of the model characteristics.

~ The lowly diode and transistor has many levels of complexity for each model described elsewhere in this channel. Stay tuned-in and search.

Keep in mind, your load and all parasitic capacitance, inductance, and ESR for every component including traces, connectors, and cables and include those estimate when using Falstad.

Here I assumed an extremely small lithography perhaps with a saphire substrate, such that the transistors had negligible capacitance and by increasing input bias current, and reducing the 30 pF to 1 pF , the 741 now has 100 MHz BW ! (lol)

Using Labelled Nodes, the Feedback resistors are added for 60 dB gain and the input Vio is approx. +60 uV. So you can see the capability of the 741 is not from schematic design but the performance of each transistor.

I can sell these to @Audioguru if he wants to order 100k. ;)