I need to design a common emitter amplifier for my next electronics laboratory.

Specifications are the following:

- 1 mA of collector current

- Load resistance of 1k ohms

- Voltage gain of 10

For 1mA, $$ \beta = 185 $$ according to the datasheet. So to fulfill these requirements, I made a system of equations to obtain the values of the resistances. First I wrote the biasing loop equation: $$15\ V=10^{-3}R_C+\frac{185+1}{185}10^{-3}R_E+10\ V$$ Where I chose $$V_{CE}=10.$$ Simplifying I obtain: $$ R_C +1.005R_E=5000$$ Next I wrote the equation for the common emitter amplifier gain, and equated it to -10. $$-\frac{\beta \ R_C \parallel R_L}{r_{\pi}+(\beta+1)R_E} =-10$$ Where $$ r_{\pi}=\frac{V_T}{I_{B}}= \frac{26 \text{ mV}}{5.405 \ \mu\text{A}}=4810 \ \Omega $$

Replacing the values I obtain the following equation: $$ 185 \frac{\frac{1000 R_C}{1000+R_C}}{4810+186 R_E}=10 $$ Using Maple I obtained: $$ R_C=4942.8 \ \Omega, \quad R_E=56.86 \ \Omega $$

For the rest of the resistors I used the voltage divider relationships for biasing, obtaining

$$ R_{bb1}=20797 \ \Omega, \quad R_{bb2}= 1114 \ \Omega. $$

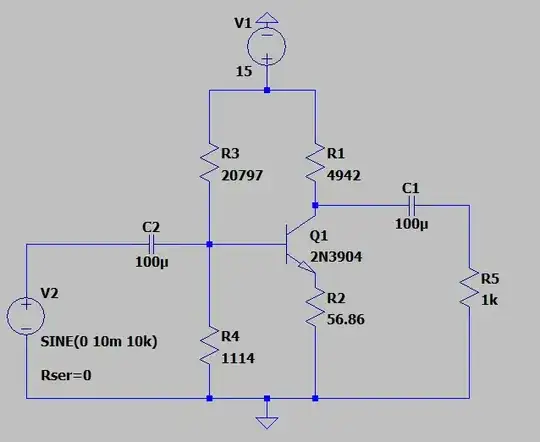

Then I simulated the following circuit in LTspice:

For the gain, I obtain approximately 11.184 which is in the margin of error. Problem is, when measuring the DC operating point of the collector current, I measure 1.6 mA instead of 1. I am kind of stuck, I don't know where I made a mistake.