"Complementary gates are inverting, non-inverting functions need an inverter" is something I see in almost every CMOS gate resource, but I don't understand why at all. I feel the math behind why would make it more intuitive, but I can't find any clear explanation.

-

because for a CMOS pair, a high input causes the output to be low. – tobalt Oct 03 '21 at 09:45

-

Nothing to do with the maths, but the practical details of amplification. https://electronics.stackexchange.com/questions/203605/what-is-the-point-of-converting-everything-to-nand-nor-and-how-do-you-do-it-righ/203612#203612 – Oct 03 '21 at 12:27

1 Answers

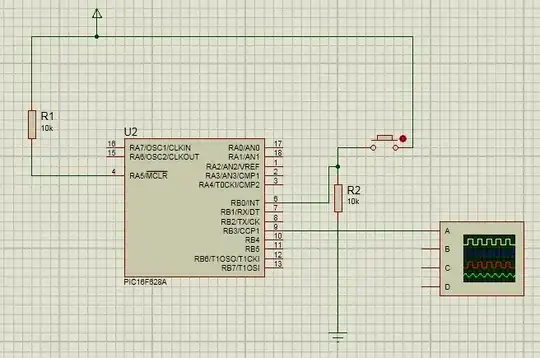

The complementary pair at the output of a CMOS gate is circuit "C" here:

simulate this circuit – Schematic created using CircuitLab

As you can see, it might be considered to be a merging of circuits "A" and "B", where we replace resistor R in "A" with the MOSFET from "B", or vice versa., and tie the gates together.

In circuit A, when In (the gate voltage) is high, the transistor is on, pulling OUT to a low potential. Otherwise, with IN low, the transistor is off, and OUT is pulled up rather weakly by R.

By contrast, for circuit B, the MOSFET is turned on when IN is low.

However, both circuits A and B, are inverters, where:

$$ OUT = \overline{IN} $$

Given that circuit A is really good at sinking current into its output, but poor at sourcing, with the associated sluggishness in transistion of OUT from low to high, and that circuit B suffers the exact opposite failings, it makes sense to combine the two into a single output stage that can sink and source very well. That's what circuit C is, a pair of complementary NMOS and PMOS transistors, able to sink and source well, and to provide fast rise and fall times at the output.

Nothing else changes, though, and the relationship between IN and OUT is still \$ OUT = \overline{IN} \$, so we can say that a complementary pair output stage is still an inverter.

It is important to note that in all three ciruits above, the transistors are connected in "common source" configuration, giving rise to signal inversion. Perhaps you have been confused by circuits that look like this:

In that circuit, it is the drains that are connected to the supply rails, not the sources. In this "common drain" configuration, each transistor is a "source follower", which does not invert the input signal. This system is not used in CMOS logic devices, and is mainly used only for analogue applications.

To illustrate this, below I compare the behaviour of an N-channel MOSFET in common source configuration (top) with common drain (bottom):

There are a few points to notice in the graphs of output voltage vs. input. Firstly, the common source version (top) exhibits a sharp output transition from high to low, very "digital" in nature, with a clear threshold. The gradient of that slope is the voltage gain. Higher is better, for cascaded digital stages, to avoid attenuation from stage to stage. The common drain setup, in comparison has a voltage gain (slope) of 1, which is a problem when you want outputs slammed all the way up to Vdd or all the way down to ground.

Secondly, as I just mentioned, the common source output (top) extends almost to ground and the positive rail, which is exactly what you want in the digital domain. Compare that with the common drain (bottom), where the output voltage is always 3V or so less than the input. It can never actually reach the positive supply potential unless the gate is driven 3V beyond the positive supply. This is a deal breaker for digital circuitry.

Lastly, it's pretty clear that the common source version inverts the signal, while the common drain does not. Since CMOS output stages are common source, that's why they are to be considered inverting.

- 27,759

- 2

- 16

- 87

-

Good answer, but your last sentence is quite the cliffhanger. Maybe add a little bit of "why" ? – tobalt Oct 03 '21 at 11:11

-

Your final circuit example, with the source followers, does not make sense in CMOS logic design. The transistor bodies **are not** connected by default to source or drain. Your circuit suggests that the bodies of the transistors would be connected to the output....that never happens. – Elliot Alderson Oct 03 '21 at 11:46

-

Hey @ElliotAlderson, fair enough. I wish I had the right symbols in CircuitLab. I think the main points are good, and the question is answered. I also did say that we don't use source followers in logic - have I misunderstood you here? – Simon Fitch Oct 03 '21 at 12:00

-

1@tobalt Well, I added a section comparing common drain and common source, but I got shafted by the old "duplicate question closure". – Simon Fitch Oct 03 '21 at 12:02