I am trying to implement a function using only NAND gates. I know I can simply use

but my book never mentions such a thing like above. This is a question from my book and I don't understand how I am suppose to go about doing something like this. I know De Morgan's theorem is (X + Y)' = x' * y' but I do not understand how this is useful to me. I know how to create kmaps and make minterms and maxterms and create circuits and all about the truth tables but how would I go about implementing a NAND gate in any function.

From the truth table I have the terms x1 x2' x3'+ x1' x2' x3+ x1 x2 x3+ x1' x2 x3 and I know how to create the circuit for this using OR and AND gates but how would I go about implementing any NAND gates in any circuit? Why is this useful? Why wouldn't I just use a NOT gate instead? Why was this gate invented?

Ok after looking at Making a logic circuit with only NAND GATES? I have a great understanding of how to create these gates but like I mentioned before why is this gate useful why wouldn't I just use a NOT gate instead?

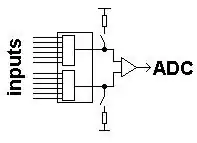

Somebody thinks I am just trying to do homework so here is the solution to the problem