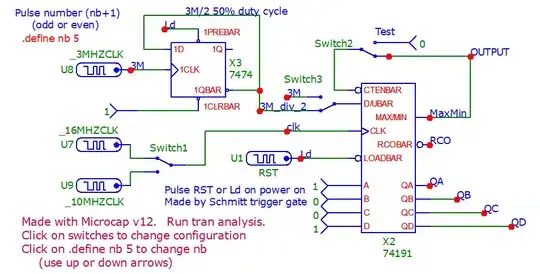

The trouble with using \$\overline{Q}\$ as the main output is that you rely on the monostable being triggered as soon as power is applied, to bring \$\overline{Q}\$ low. Then you keep retriggering as the leading edge of each input pulse arrives.

You may get lucky, and have the device power-up in a triggered state, as explained in "11.2 Power-up considerations" on page 13 of the Nexperia datasheet. Otherwise though, if the 74'123 starts in an untriggered state, \$\overline{Q}\$ will be high at power-on, and the only way to automatically trigger the monostable (bringing \$\overline{Q}\$ low) will be to provide some trigger signal as soon after power-on as possible.

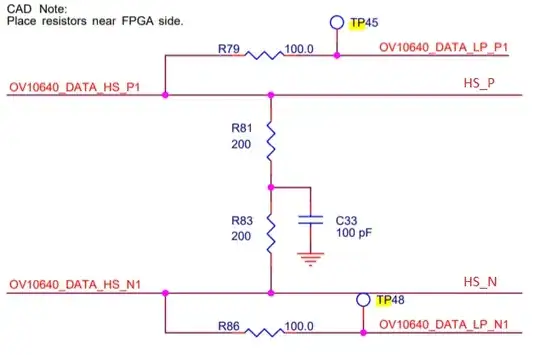

For this reason, \$\overline{Q}\$ will require external gating, if you wish to guarantee a low output at power-on, like this (I don't show timing elements \$R_{EXT}\$ and \$C_{EXT}\$, to keep it clear):

simulate this circuit – Schematic created using CircuitLab

C1 and the AND gate ensures that OUT stays low for a period of approximately \$R1 \times C1\$ seconds after power is applied. D1 discharges the capacitor immediately upon power-off, and prevents a negative voltage at the top of C1 from damaging the AND gate input. D1 may not be necessary if the AND gate already has input protection diodes.

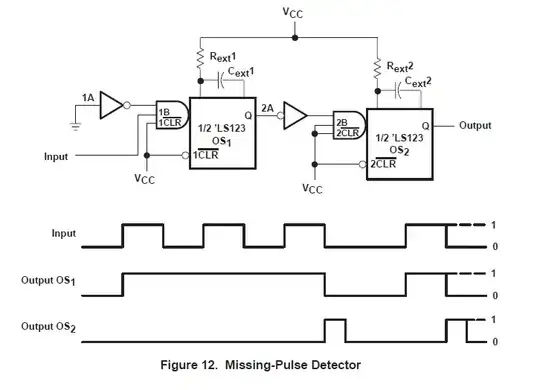

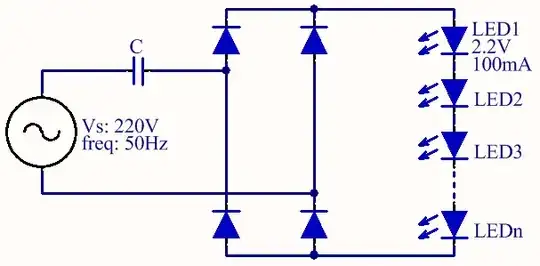

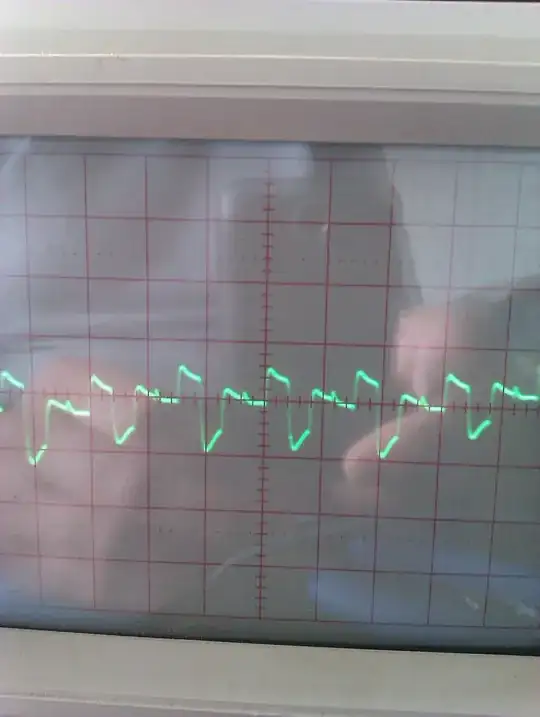

A second problem you may encounter is that the output \$\overline{Q}\$ will go high only until the next incoming pulse. If the pulse is only a little late, then you may find that the output will go high for mere nanoseconds. On page 11 of the TI document "Designing with the 74LS123", they have a "missing pulse detector" circuit which uses both monostables of the 74'123 to overcome this problem. They use the second unit to provide a fixed-length pulse, regardless of the duration of the output pulse of the first unit:

This circuit has the fortunate side-effect of eliminating the problem of an initial high output, because it relies on the falling edge of OS1's Q output to trigger the second unit OS2. You use OS2's Q output, which you know will be low at power-up.

It still suffers from the ambiguous start-up state, but this can be solved with another RC power-on delay to force both units to start up in the untriggered state, as described on page 13 of the Nexperia datasheet:

simulate this circuit

The above solution also requires only a single IC, which is a bonus. You mentioned activating a relay, so this above solution will also permit you to activate it for some known, controlled period of time, independent of the duration of the detected anomaly.