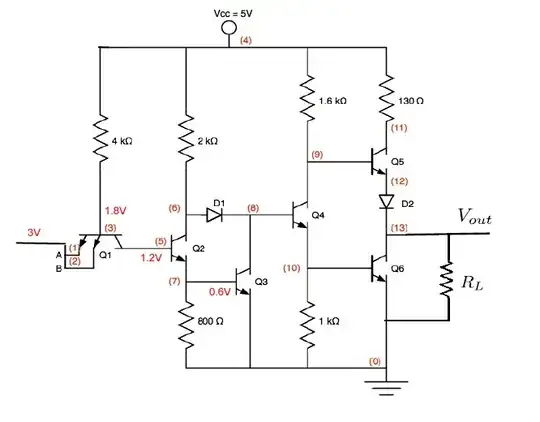

Consider the following logic circuit:

Approach:

Consider the following 2 cases:

- Any , or both the inputs are low (0 V): The base of Q1 will be at

0.6 V. A current1.1 mAflows through the4Kresistor to the base, which saturates Q1. Hence the collector is at0.2 V. Also, I don't think there will be any collector current, which means Q2 is OFF, which further implies Q3 is also OFF, since Q2 will have no collector current (== Q3 will have no base current).

If Q3 is off, then the current due to the 5V supply flows through the diode D1 into the base of Q4, which means Q4 is ON. Now the collector current from Q4 enters the base of Q6, hence Q6 is also ON.

The emitter of Q6 is at 0 V, hence the base of Q6 is at 0.6 V==emitter of Q4, hence the base of Q4 is at 1.2 V, which means the P side of D1 is at 1.8 V. Also, The collector Q4=== Base of Q5= 0.8 V. If we assume D2 to be forward biased, then this will mean the emitter of Q5 is at 0.8 V, which means Q5 is reverse biased. This suggests that the collector current should be 0 == current through .130K resistor. The simplifications look like this:

Clearly, Vout=0.2 V (LOW), and a current 0.2/RL = 0.01 mA flows through the RL. However, the issue I have with this is , with Q5 OFF, I really cant properly visualise how current can flow through RL. Since with Q5 off, there is no emitter current, so no current through the diode.

Also, I can't seem to properly reason why Q2 will be OFF.

- Both the inputs are high (

3 V): If we trace back the voltages from Q3, and assume the base-collector junction of Q1 is forward biased we get these voltages:

So the base-emitter junction of Q1 is reverse biased and there is no emitter current, Hence collector current = base current in value, and the collector current flows out of the collector, into the base of Q2 which turns on Q2,which implies Q3 is also ON. Now I am not really sure why, but if we assume Q4 to be OFF, this will imply Q6 is also OFF, and also, Q4 being OFF implies the base of Q5 is pulled high so Q5 is ON.

This is the final situation. Considering Q5, the currents can be written as: \$I_{c} = 5 - (Vo + 0.8)/.130\$ mA, \$I_{b} = 5 - (Vo + 1.2)/1.6\$ mA, \$I_{e} = Vo/R_{l}=Vo/20\$ mA. Using Ie= Ib+Ic, we can solve for Vo, and we get \$Vo=4.145 V\$, i,e HIGH. So it seems that this circuit is behaving as an AND gate, and we have more or less calculated all the currents, now that we know Vo.

My final questions:

Why is Q2 OFF in case 1?

Given Q5 is OFF, how from where exactly can we expect a current flow of 0.01 mA through RL in case 1?

Can the collector current (Q1 of case 2) really flow out of the collector?

Why is Q4 OFF in case 2?