Your questions

See this detailed discussion for fuller answers. But in short:

Do note that the trigger voltage set by \$R_1\$ and \$R_2\$ is also a Thevenin voltage source with a Thevenin resistance. When the capacitance is charging, no real current is being drawn from it so the Thevenin voltage appears at the gate, unscathed. But, once the triggering threshold is reached (slightly above the Thevenin voltage of the resistor divider) the PUJT momentarily connects the anode to the cathode (with some voltage drop, of course) and starts the capacitor discharging. So long as the resistor charging the capacitor is large enough that it cannot meet or exceed the minimum valley current (about \$70\:\mu\text{A}\$ for the device shown given the Thevenin of \$R_1\$ and \$R_2\$), it will oscillate. In this case, \$R_4\$'s current cannot possibly exceed \$20\:\mu\text{A}\$. So that's good. Also, the Thevenin divider resistance is now supplying substantial current (not like the capacitor.. but substantial) and therefore there is a significant voltage drop across them and therefore the gate voltage has become much lower, very quickly. For more details, please read the detailed discussion I just mentioned, earlier, and examine the curves there, too.

Aside from the fact that for the device mentioned their equation for \$V_A\$ doesn't use the datasheet value (or name, which is \$V_P\$, I think) but instead just uses a standard diode drop, I've no idea where they got that equation. The peak current is going to be huge because that capacitor is discharging into a \$47\:\Omega\$ resistor. Given that circuit, getting close to a quarter-amp, or so. If you multiply a quarter-amp by the sum of \$R_1\$ and \$R_2\$ you'd get an unimaginably high voltage value for that voltage difference in the numerator and... well... it makes no sense. I had considered the idea that maybe they were talking about the current into the gate when the capacitor is finally discharged enough that the PUJT is going to reset. But that idea doesn't produce their equation. Looks like a current. It takes the current through \$R_1\$ and \$R_2\$ when the PUJT isn't firing and subtracts from it the threshold voltage divided by those resistors (roughly.) Must be something they were thinking about. I just don't know what.

See below and pages referenced therein.

That book

I've been surprised, at times, by errors in "Practical Electronics for Inventors", despite some respected names contributing to it. This page has now become yet another.

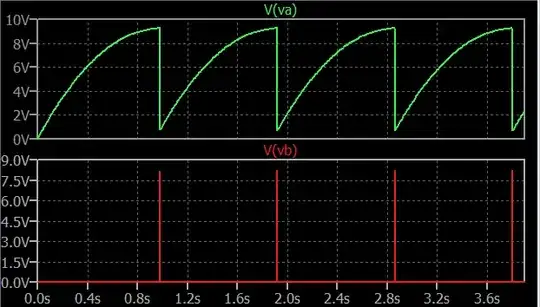

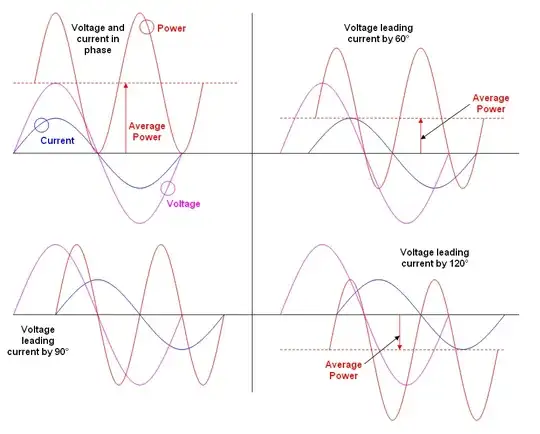

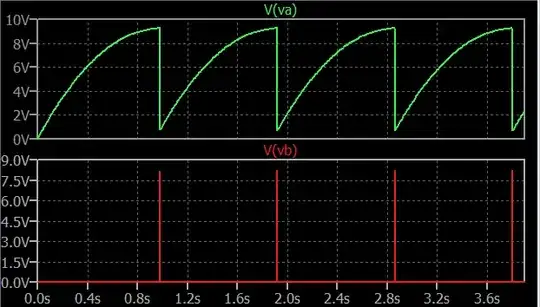

The top curve makes perfect sense. It's an RC charging curve. Just what you'd expect from \$R_4\$ and \$C_1\$ without the attached PUJT anode. Should be on the order of \$\tau=R\,C\approx 1\:\text{s}\$.

Aside from errors highlighted by your second question, it's also now the bottom curve that bugs me. No idea where that comes from. It suggests a rising voltage during the pulse. Where would that come from? Not \$R_1\$! It's value is too big. \$C_1\$? No, that's discharging into \$R_3\$. A discharge curve doesn't look like that. So... what's up? Where's the discharging behavior, especially after all that effort to demonstrate the charging curve?

Well, it was probably too short to show, to scale, because the charging period is long while the discharge period is very short. So perhaps they just got an artist to "wing it?" No idea.

Here's what it really looks like:

And zoomed in a lot, you can see what the discharge curve actually looks like (in red):

Well, what do you know? It really is a discharge curve! Who would have thought that from reading that book?

Burn the book, I say.

Without a single doubt

We'll smoke the monster out!

A few lines from a scene in the old Alice In Wonderland movie.

PUJT model

The two BJTs, if you try and use them that way to make a PUJT, need to have certain parameters in relationship to each other or the whole thing doesn't work right. It's better to just use a .SUBCKT card if you can find what to put into one.

In the case of the 2N6027 and 2N6028, I've have these 'reasonable' PSPICE models:

.SUBCKT 2N6028 1 2 3

* anode gate cathode

*node: 1 2 3

Q1 2 4 3 NMOD

Q2 4 2 1 PMOD

.MODEL NMOD NPN(IS=2E-15 VAF=100 IKF=0.3 ISE=2.5E-12 NE=1.6 RE=0.15 RC=0.15 CJE=7E-10 TF=0.6E-8 CJC=2.2E-10 TR=4.76E-8 XTB=3)

.MODEL PMOD PNP(IS=22E-15 VAF=100 IKF=0.3 ISE=1E-12 NE=1.7 RE=0.15 RC=0.15 CJE=7E-10 TF=1.6E-8 CJC=2.2E-10 TR=5.1E-8 XTB=3)

.ENDS

.SUBCKT 2N6027 1 2 3

* anode gate cathode

*node: 1 2 3

Q1 2 4 3 NMOD

Q2 4 2 1 PMOD

.MODEL NMOD NPN(IS=5E-15 VAF=100 IKF=0.3 ISE=1.85E-12 NE=1.45 RE=0.15 RC=0.15 CJE=7E-10 TF=0.6E-8 CJC=2.2E-10 TR=4.76E-8 XTB=3)

.MODEL PMOD PNP(IS=2E-15 VAF=100 IKF=0.3 ISE=1.90E-12 NE=1.5 RE=0.15 RC=0.15 CJE=7E-10 TF=1.6E-8 CJC=2.2E-10 TR=5.1E-8 XTB=3)

.ENDS

If you use these, I believe you'll find they work reasonably well when used in a Spice program. (Also see this answer for a symbol that can be used in LTspice.)

Just use regular BJTs

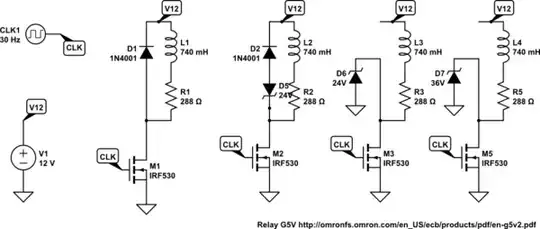

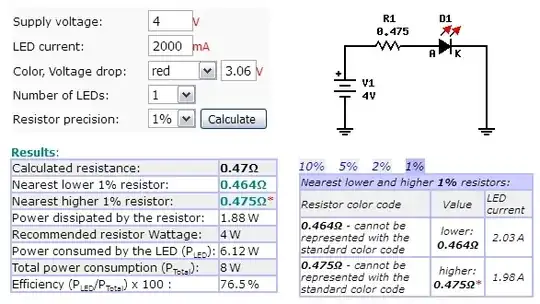

You can fabricate a kind of fake PUJT without actually having to own one. But the design is... slightly different. Here's the resulting output of the one I'll draw, shortly:

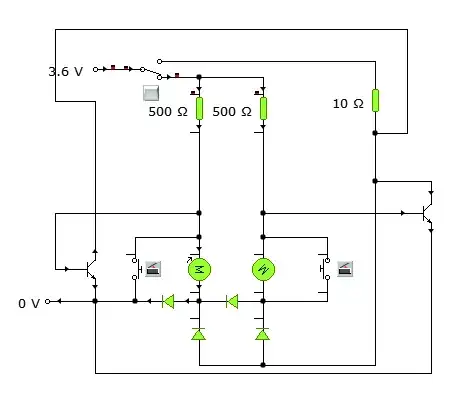

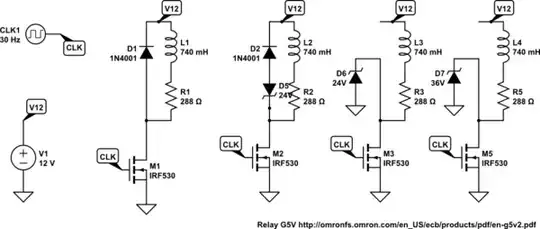

Now here's the schematic. As you can see, it's similar. Nice thing is that it works with "regular" junk box parts and it is modestly temperature-stabilized regarding the threshold voltage.

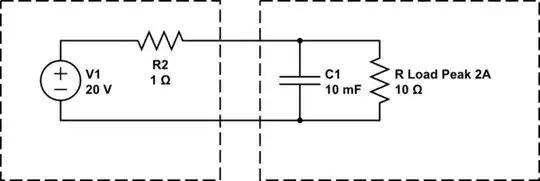

simulate this circuit – Schematic created using CircuitLab

Over on the right you can see how the PUJT is often diagrammed out, in books, using two BJTs. It's just that it is kind of tricky to actually drive that beast well, when the BJT parameters are coming from your junkbox (and wired together using copper) instead of from some FAB design lab (and directly sharing junctions.) If interested, take a look here for a short discussion about that generalized BJT version. You'll see something similar to the above there. But... there are some notable differences, too.

It's a heck of a lot easier to just buy some PUJTs. Do it soon. I don't know how long supplies will last! (Is anyone still building them? I have my lifetime supply. Do you? ;)