This question is (loosely) related to my previous question here.

I wanted to check the ESD protection diodes of the LPC1114 MCU from NXP. So I measured all pins on a brand new LPC1114 MCU with a multimeter in diode test mode and I am confused about the results.

Measurement setup 1:

- Connected red (anode) multimeter probe to VCC

- Connected black (cathode) multimeter probe to GPIO (e.g. Pin1 PIO2_0) ==> Result ~1.2V

Measurement setup 2:

- Connected red (anode) multimeter probe to GND

- Connected black (cathode) multimeter probe to GPIO (e.g. Pin1 PIO2_0) ==> Result ~0.54V

(When I reverse the measurement polarity, I get a open circuit reading)

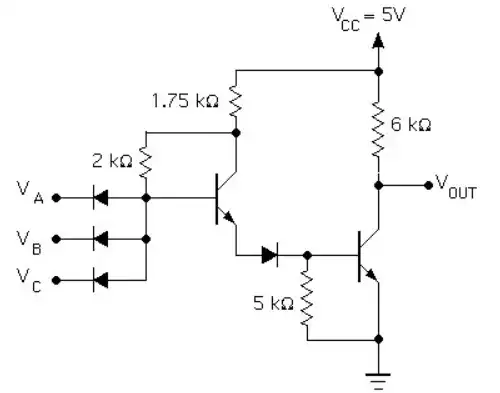

What I don't get is why in the first measurement the cathode seems to be on the GPIO side?

For a proper circuit protection, I would expect the cathode of the supply protection diode to be on the VCC side.

Edit1: I made a mistake and made the measurements when the MCU was still soldered on a PCB. So I removed the MCU and got the following measurements (my multimeter diode test has Vo=3.75V and Io=0.6mA)

I think this brings it back to what I was expecting: A diode from GND to PinX and a diode from GND to VCC (although the diode from PinX to VCC seems to be missing).