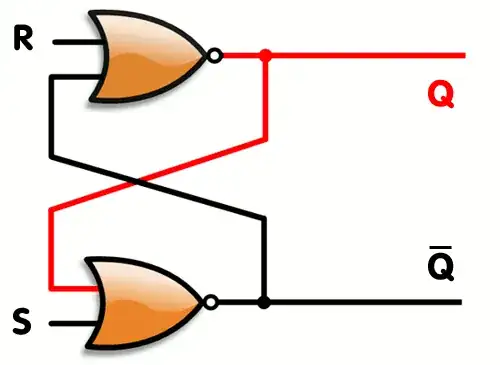

Ok this is probably a basic question, but I understand how SR latches work except one thing.

In the R input and S input you can make them 0 or 1.....but what about the input lines next to them (That rely on the output of the R or gate or S or gate)......what do those "Start" out as.

I assume it's Zero.....but with the very first clock signal (To R or S)....it hasn't gotten the output line from the other OR gate yet...so how can it get a first output.

Like lets pretend the first clock signal is R=1 and S=0 ....what about the R or gates input line next to it (that relies on the S OR gates output).....how can it get this on the first "input" signal. It confuses me?

Do we just assume it's zero or what?

edit: Since the question is confusing, the Input line RIGHT below the R (They both go into the top OR gate, im talking about the one right below it). Since it is dependent on the S output....if it's the first "Clock" signal...what would it be set to? Zero? Since obviously it has to wait for the output of S before it can actually be set to anything...but initially what is it considered.