With no input signal there's still the DC operation going on. The feedback forces all currents and voltages to settle to those values which generates to the load same voltage which is at the base of Tr2 - that's 0V, fed through R1.

You should know, that the circuit is essentially a non-inverting amplifier made of an operational amplifier. I mean this (Wikipedia image):

The opamp is in your case made of discrete transistors for high enough output power. All of its transistors except the output transistors conduct all the time for proper class A operation - no clipping as long as the amp is not overdriven.

The voltage gain is (1+Rf/Rg) . In your version the effective Rf is reduced at higher frequencies by C7. You see there's also another miniscule capacitor C3 in VAS. That also affects to the frequency response. Those small capacitors have common role. They are there to prevent your amp oscillating. Oscillating would mean full power continuous output at high frequency, for ex at 30kHz.

To fully know the subject you should learn what frequency compensation of feedback amplifiers means and how it's done in terms of rigorous circuit mathematics. Every opamp application theory book above hobbyist level contains it. The qualitative explanation can be found also in many hobbyist level texts.

Your current limiter can be designed to work. But it's not simple. Know that your drawn starting sketch of the limiter tells nothing of what actually works. It also doesn't tell where you thought to connect the wire ends. You should search for earlier tested and working full solutions. You can easily cause stability problems, a short circuit to elsewhere and overheating.

I would insert for limiting 2 things:

an audio input limiter which reduces the gain if the signal peak rises too high. That prevents distortion which easily blows tweeter speakers which do not have own amps but are connected to the same output through high pass filters.

a fast enough working fuse or other circuit breaker which stops DC voltages in case of a short circuit. A current limiter in the output stage generates distortion in too high input case and can blow the tweeters.

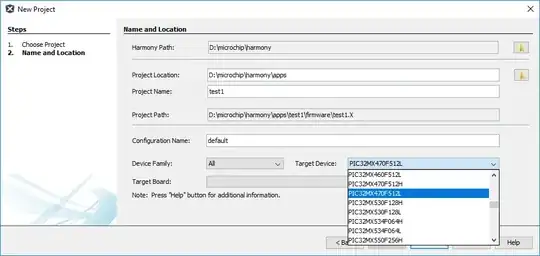

As suggested by others, run simulations. Get some capable enough program. Component manufacturers like Texas Instrument or Linear Technology offer good ones. There's also an independent previously high priced item Micro-Cap. The developer of it has retired and gives now his masterpiece for free. The latest version is v12. I use a much earlier version (=v10) because it seems to fit better into my legacy computer. Micro-Cap knows numerous components, but of course, there's no newbies without inputting the model parameters or building a macro model.

ADD1: The updated output current limiter may work but it causes distortion at high levels. The harmonics can blow the tweeters. It causes also very bad distortion at low levels because transistors are non-linear in low voltages. Quiet sounds are like a saw. The aural effect is the same as zero-crossing distortion in badly biased class B amps.

In addition if your speaker has short circuit it prevents the fuse blowing. The output transistors (Tr7,Tr9) can overheat or get destroyed due secondary breakdown. You see the safe operating area in power transistor datasheets. Simulate! It's useful.

ADD2: After you labeled the problematic currents in the image

The currents taken by the halves of the current mirror are not the same in submicroampere resolution. The base currents are taken from IcQ3. The balance state of your feedback amp has some Ivas as you have simulated.Check the Vce voltages of the current mirror transistors and their emitter resistance currents. I guess there's some difference. Current mirror is not at all steep and exact with low Vce voltages.