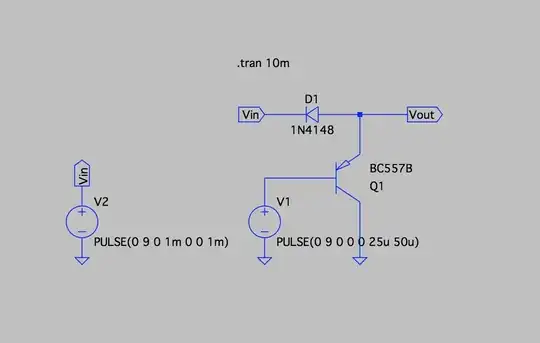

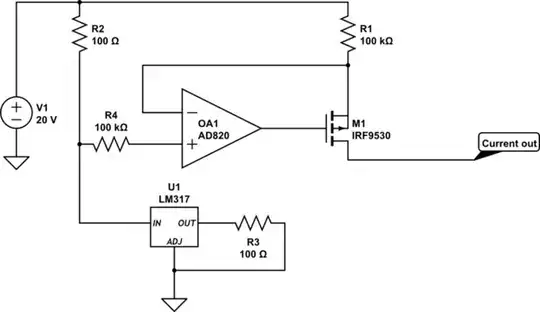

I want to convert a 3V3 PWM (10 kHz) signal to a 0-5V analog DC signal using transistors only (no DAC), if possible. The output logic should be non-inverted, i.e. 0V->0V and 3V3->5V. The time constant of the conversion should be <20 ms.

Which circuit topology could be used to achieve this?

EDIT: I have a 5V supply available.