I am trying to place multiple ring oscillators using XDC macros. I have been able to follow the steps on the video by Xilinx on XDC macros and it worked.

However, I am facing errors and critical warnings when I am trying to run implementation even though the synthesis was successful. I don't know how to solve them. I have 3 modules, one is the top module and the other two are the Ring oscillator and ring counter module.

Below are the error messages:

[DRC MDRV-1] Multiple Driver Nets: Net u4/w14 has multiple drivers: u4/w14_inferred_i_1/O, u1/w14_inferred_i_1/O, u2/w14_inferred_i_1/O, u3/w14_inferred_i_1/O, and w14_inferred_i_1/O.

[Vivado_Tcl 4-78] Error(s) found during DRC. Opt_design not run.

**Critical warnings:**

[Synth 8-6859] multi-driven net on pin w14_inferred_i_1_n_0 with 1st driver pin 'u1/w14_inferred_i_1/O' .

[Synth 8-6859] multi-driven net on pin w14_inferred_i_1_n_0 with 2nd driver pin 'w14_inferred_i_1/O'

[Synth 8-6859] multi-driven net on pin w14_inferred_i_1_n_0 with 3rd driver pin 'u2/w14_inferred_i_1/O'

[Synth 8-6859] multi-driven net on pin w14_inferred_i_1_n_0 with 4th driver pin 'u3/w14_inferred_i_1/O'

[Synth 8-6859] multi-driven net on pin w14_inferred_i_1_n_0 with 5th driver pin 'u4/w14_inferred_i_1/O'

Below is the code where I call 5 Ring oscillators in the top module:

`timescale 1ns / 1ps

module top(countreset,reset,en,enable,count,out2,clk);

input countreset;

input reset;

input en;

input enable;

input clk;

//output [31:0] count;

output [15:0] count;

output out2;

ila_0 debugger(

.clk(clk),

.probe0(count),

.probe1(out2)

);

ring_osc u0(.enable(enable)

, .out(out2));

ring_osc u1(.enable(enable)

, .out(out2));

ring_osc u2(.enable(enable)

, .out(out2));

ring_osc u3(.enable(enable)

, .out(out2));

ring_osc u4(.enable(enable)

, .out(out2));

ro_counter fgh(.reset(reset),

.countrest(countreset) ,

.ena(en) ,

.count(count),

.clk(out2));

endmodule

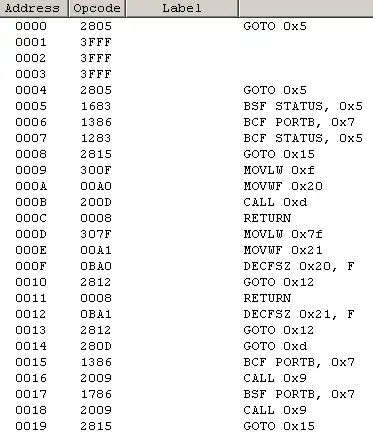

Below is the schematic if this helps.