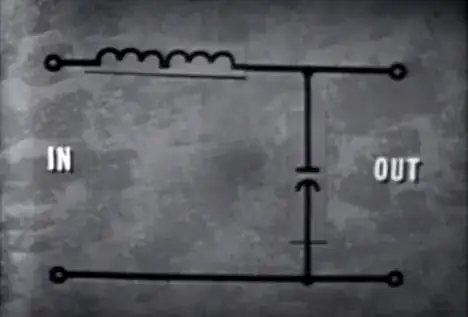

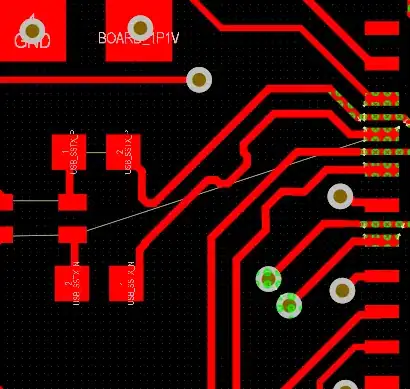

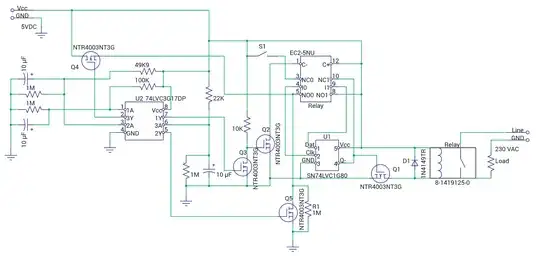

I'm working on a PCB with a USB 3.0 controller (TUSB7320, Texas Instruments) with SuperSpeed signals and High Speed Signals. There are some specific requirements about impedance and length matching. Until here all ok, but I have requested a budget for the PCB control impedance manufacturing, and a "problem" appears. The manufacturer tells to me that I have to minimize the places where the impedance traces are not controlled: vias and accordions. How can i minimize the impedance on that places?

I have other problem: the 3W rule by Texas Instruments. They recommend 3 times the trace width between trace center and trace center, until here all ok. But, to reach the impedance profiles (100 or 90 ohm) I have to make bigger the width of the traces, reaching 0.22 mm or 0.2 mm. Have i to introduce 0.6 mm or 0.66 mm between this traces and nearby traces? Which rules are stronger?

EDIT: I add images about my design.