Below is the verilog code that I wrote to implement a simple SR Latch. Note that I assumed different gate delays for the same NOR gate. (#10, #5)

module rs_latch(

input S,

input R,

output Q,

output Q_L

);

assign #10 Q_L = ~(S | Q);

assign #5 Q = ~(R | Q_L);

endmodule

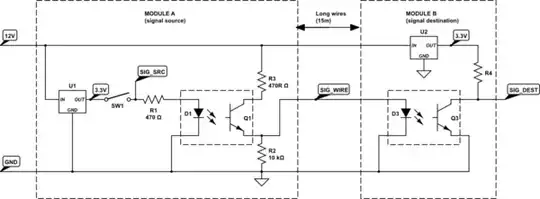

I expected Q and Q_L would oscillate right after 500ns, when both S and R are changed to 0. When the gate delays were the same #5, they did oscillate. However, in this case, as you can see from the image below, it is not oscillating.

Below is a hand-drawn diagram that I had expected to appear.

Could you please explain why it is not oscillating?