I want to switch upto 36V and higher onto a piezo disc. Wideth of the pulse I want to apply is 250 nano-secs.(4 MHz - piezo resonant frequency )

I summarise the problems I face here.

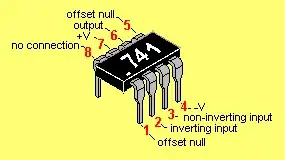

I apply the pulse using monostable multi-vibrator,74hct221d and ne555 and passing it through 74hct14d.(These are not seen in the simulation.) I plan to use psmn041-80yl mosfet to switch as it can accept a 5V gate supply.

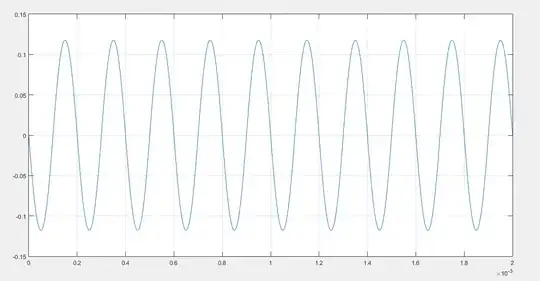

74hct14d can at the maximum supply upto 20mA load which is not adequate for the mosfet gate which needs in the least a few 100mA to switch in nano-secs. I tried using a fast transistor mmbt4403 for supplying increased current to mosfet gate. It is switching, it introduces a long turn-off delay, as it has a high storage time of 225 nano-secs. So, in spice simulation, I could not get better than 1.2 us switching time using 250 ns trigger signal. (This switching time is at the gate of the mosfet - see draft2 circuit and draft2-output).

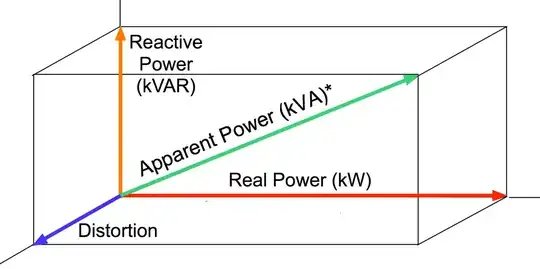

Using a NMOS to switch at 5V logic and PMOS to switch at 36V power, I get result like draft1.png. Even in this case, it must be mentioned that the gate current spice simulation shows a couple of hundred mA, which cannot be supplied by 74hc14d.

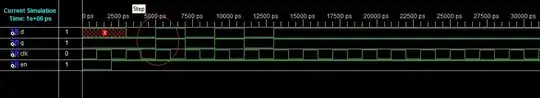

If I directly apply 250ns pulse to the gate (for proof-of-concept - see draft3 circuit and draft3-output) in spice-simulation, I get about 300 ns switching time on mosfet which is manageable.But this cannot be done due to 74hc14d output current limitation.

And I cannot supply enough power to mosfet gate using a 5V logic, so cannot switch it without enhancing gate-current. Enhancing gate current with transistor or signal-mosfet introduces unacceptable delay. What options I have ?

I have seen related questions and answers and my simulations already try them out. I need help which addresses nano-secs switching. Thanks in advance.