This was posted a while before the OP added a lot of details to their question in little steps. Crucially, adding that the ED_PIN output is open-drain, then changing their circuit from using a MOSFET stage. I will leave this answer as it covers MOSFET switching capacitance.

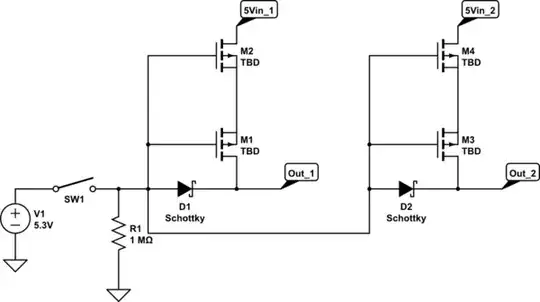

The MOSFET has pin-to-pin capacitances. You'll find them specified in its datasheet, along the lines of Cgd/Cgs/Cds or Cis/Coss/Crss.

Even in a small MOSFET, these capacitances play a part and in larger devices they can have a significant effect on the circuit around them.

First: Cgs

Here, the low/un-charged MOSFET gate-source capacitance Cgs present an instantaneous short to ED_PIN when that pin switches from LOW to HIGH. Therefore you should always use a gate series resistor to limit this current while the gate charges.

Not doing so can weaken the long-term reliability of the logic output but that very much depends on the logic IC and the output stage circuit within it. However, I would always do so to remove the effect of transients generated by switching a capacitance.

The gate resistor value is determined by the GPIO maximum output current, so that with 5 V at the GPIO and 0 V at the MOSFET gate, the resistor current is less than the GPIO max. output current. When you calculate all of these, you must take the tolerance of the 5 V supply, GPIO specs and resistor value into account - don't just use these nominal values. Guess example value might be 1K2 but don't use that, calculate your own.

Second: Cdg

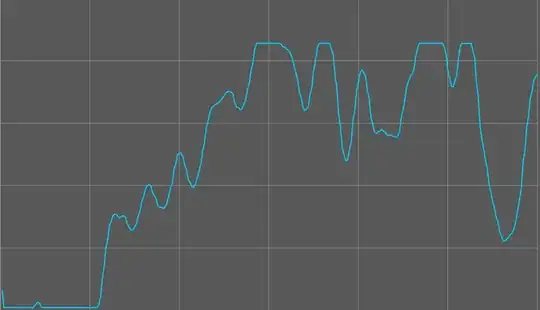

Next, when the MOSFET is switched off, the drain will be at 1.8 V and the gate, say, <0.2 V so Cdg will be charged to, say, 1.6 V. When the MOSFET gate goes HIGH, the drain will go to almost 0 V and the circuit will try to drive Cdg to around -5 V. So Cdg can produce a transient at its gate.

The gate series resistor will reduce the effect of this transient on the ED_PIN.

I have seen this effect several times, as the wisdom of logic gates driving FET gates is a common mistake. A recent board of someone else's design had logic IC outputs driving the gates of MOSFETs switching light off-board loads connected through cables (inductances). The MOSFET Cdg was sufficient to knock the logic gates over and stop the system working. I had some time with a scope' to verify then added gate series resistors and the system worked reliably from then on.

This could be the cause of your problem, could not be, and you keep editing your question and adding information. But I recommend you add the gate series resistor to remove a potential problem as well as your actual problem.

Please understand that the i.MX6 processor and the pullup resistor are elements of a product on which the less modifications are made, the better.

Please understand that the i.MX6 processor and the pullup resistor are elements of a product on which the less modifications are made, the better.