I have been recently trying to understand how the STM32 ICs should be routed on PCB, in particular parallel capacitors of different values for power design. I have come across various suggestion about that it is legacy design, and that these capacitors should be replaced by only one because of anti-resonance problem.

So checking out the native design of STM dev board should provide insight of the right approach. Luckily everything is provided on STM website. PCB files are from Altium Designer.

Looking at design one interesting thing appeared evident when different capacitor values should be side by side. On schematics the 1uF is used in parallel with 100nF:

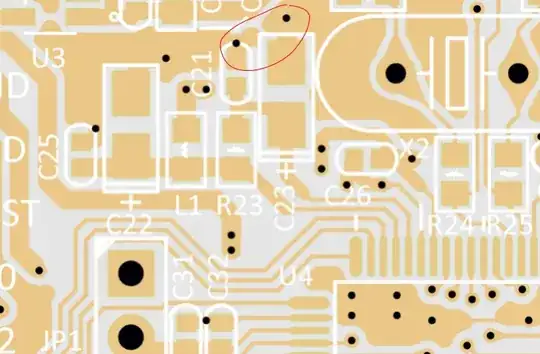

The way how it is routed can be seen on the picture bellow.

- Whats interesting is the separation of ground connection between C21 and C23, which is only connected through bottom plane, but could be easily connected on the Top plane aswell. This seems to be consistent when it comes to other capacitors, at least by trying to introduce some larger path in between.

Why thats the case?