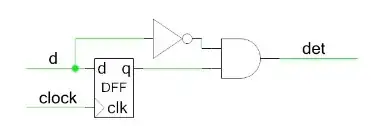

I have a falling edge detector built based on a D flip-flop as shown in the following figure:

Components: 74hc74, 74ls04n, 74hc08

A sample output is shown below (I invert the output since I need it as an active low):

My question is why it sometimes doesn't detect the falling edge?

Thank you all so much!

The problem was the logic analyzer sampling rate and frequency as @Elliot Alderson mentioned.

I re-configured the PulseView and finally could capture the output correctly (indeed there was nothing wrong with the circuit itself)