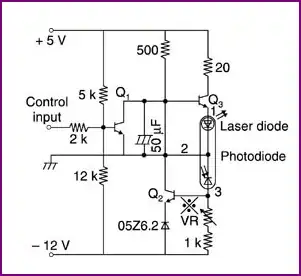

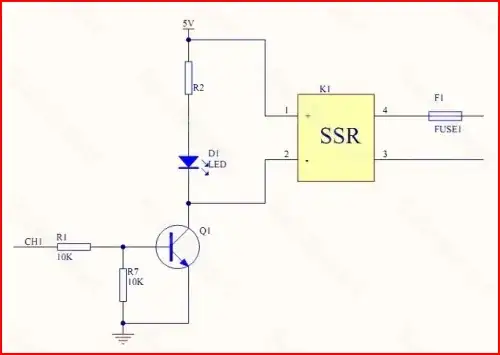

The ambiguity is in the symbols used to show an NCh FET. This one is special made from GaN.

The simplified schematic is in error. (draft-person error)

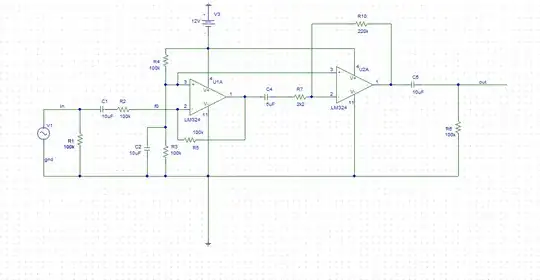

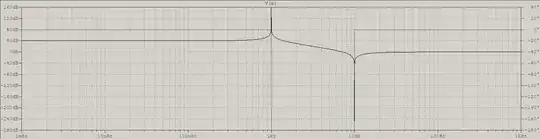

So your simulation must use the exact same parts and exact same layout to come even close to what the designer ended up with for every part!!

I don’t know the history of FET symbology but when it looks like a BJT with 1 plate for the gate and a horizontal arrow for the source going out to look like an NPN, it is not really a Pch FET as you and another answer writer believe, but rather it is a very special GaN NCh FET.

https://www.mouser.com/datasheet/2/692/GS66504B%20DS%20Rev%20160229-938232.pdf

Authors of these IEEE papers rarely show all their trade secrets with an accurate full design spec, simulation but at least a BOM is given (Bill of Material, partial)

Most of them have bugs they never admit to from parasitic instability or other issues.Yet this author is from MIT so I hope he did achieve some success on kW/kg but there is no mention of MTBF stress margins and heat rise Etc. Yet no DVT results and you never see this in IEEE papers which is standard in electronics industry, which I have done in every company I have worked for. without prior experience on these designs your chances of simulating this are slim without 3mos of dedicated work and research.

Anecdotal

My son-in-law (Prof @ U of T) has designed such inverters for DC stackable microgrids several years ago, so this is not really new technology yet novel enough because of the propulsion application.