As an introduction to electronics, I am still working my way through Charles Platt's Make: Electronics (2nd edition).

This issue is about Experiment 21: A Powerful Combination

In circuit on figure 4-107, a 7408 (quad-AND) is used to implement a simple switch based "password system". The different switches have to be pressed in a given sequence, each switch allowing to change the output of a AND gate to high, thus latching this AND and providing a high input to the sub-sequent AND gate.

(I suppose I am not allowed to post the circuit schematic from the book, as it might be copyrighted material?)

Minimal example

I have been having problems with the resulting circuit sometimes starting in the "unlocked" state, without having to first press the correct sequence of switch. By fault tracing with a voltmeter, it appeared that, sometimes, the different gates are latched in high-output at circuit startup.

Here is a minimal example showing the latching for a single AND gate:

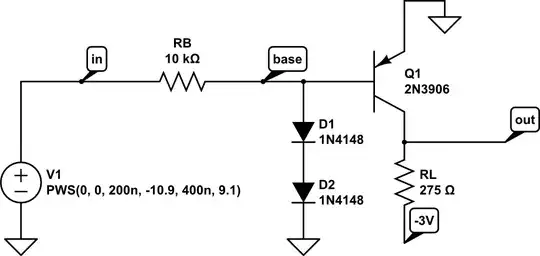

And here is the corresponding schematic (my first, please be indulgent):

simulate this circuit – Schematic created using CircuitLab

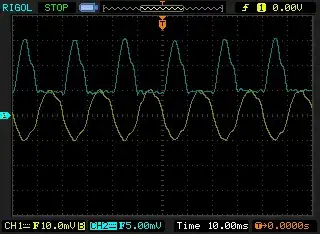

About 1 in 5 times when applying 5V to the power bus, the low-power yellow led will light up, without having to first press the switch.

Questions

- What could cause this undesired (and erratic) self-latching at startup?

- Is there a design flaw in this circuit? (or is there an obvious wiring error in my attempt to build it?)

- The book is using 74HC08, where I am using 74HCT08N. Can it lead to the problem?