I keep seeing in specs/manuals to drive a pin high or low, what does that really mean? For example I'm working with a voltage regulator that has an ENABLE pin that says will switch the board to a low power state when "Driven Low".

-

All LOGIC levels for hi = 1 and lo =0 are defined in the datasheet and usually means< < 1/4 Vdd for 0 and >> 3/4Vdd for 1 for CMOS only, because the threshold is often 50% +/-25% to 33% over all temp. range and all device tolerances. – Tony Stewart EE75 Mar 12 '21 at 18:44

-

You already have great answers and this doesn't really deserve one, but referring to high and low has the advantage of being able to discuss the logic state without considering actual voltage at all(which can be different at different parts of the system). – K H Mar 13 '21 at 12:00

6 Answers

It means that the regulator is turned on when the voltage on the ENABLE pin is set above a certain threshold (driven high) and it will be off when the voltage is set below a certain threshold (driven low).

The actual logic levels what "high" and "low" mean depend on the regulator and the levels are listed in the datasheet.

- 127,425

- 3

- 97

- 261

Instead of "Drive Low" we also say "Set Low" or "Tie Low", with the same meaning - connect the pin to a logic Low voltage - usually Ground.

Likewise, "Drive High" means connect to a logic High level - usually Vcc/positive power supply.

- 57,014

- 1

- 48

- 127

You have to read (and sometimes interpret) the datasheet. For a voltage regulator with an ENABLE input (as opposed to an /ENABLE input) the ENABLE input has to be high to enable the regulator. We know that.

What we don't know is what voltage we must apply to the ENABLE pin for it to interpret as a high reliably. We also don't know what happens if we leave the pin open. If there is a specification for "leakage" on the ENABLE pin of << 1uA and no other information we can assume the ENABLE input is very high-impedance and it needs to be connected to something. And we don't know what voltage we must apply to the ENABLE pin for it to interpret as a low reliably. And we don't know the limits of voltage we can safely apply to the pin.

You may also care if there is some hysteresis, how much etc.

If the allowable input voltage includes the maximum Vin for the regulator we can simply tie it to Vin or use a transistor and pullup resistor to switch it. The maximum value of the pullup resistor will be determined by the leakage or internal bias current from the input and practical factors and by the required Vih. If the Vih is low enough (as it often is) we can control it directly from a CMOS output (like an MCU GPIO pin), and we don't need to level shift it up to some fraction of the input voltage. But that needs to be checked.

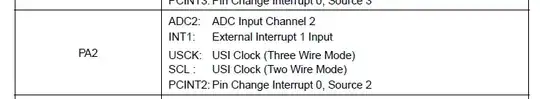

Take, for example, the HX9193 low power CMOS regulator (any images from datasheet).

This tells us that the regulator will shut down if the pin is left open.

The three columns are labeled min/typ/max here.

The ENABLE pin must be < 0.4V to have the regulator off. Since there is a nominally 1M\$\Omega\$ resistor to ground, we can't inject more than 400nA (and given tolerances, 100-150nA would be a better limit) if we want it to reliably remain off.

To have it turn on, we need to apply at least 1.4V, but we can apply any voltage from 1.4V all the way up to Vin + 0.3V. So we can connect this pin directly to a 3.3V or 1.8V CMOS output and have it control the regulator. The output will sink no current when low, and when high will source a few uA at most. Perfect.

Now compare the TI LP38855 (any images from the datasheet)

Here we see that current is flowing out of the ENABLE pin. That means that if you leave it open the regulator will turn on, opposite of the other part.

We need to give it 1.55V to have it turn on reliably (bold is over temperature) and must pull it down to less than 30mV to have it turn off reliably. Elsewhere it says we can apply 0 to Vin to the ENABLE input (and that it will "survive" 6V under absolute maximum ratings). The latter could be an important rating if Vin could occasionally be 0V while your GPIO is outputting 3.3V.

So we can connect the ENABLE input to a CMOS output 3.3V etc. but it must not drop more than 30mV when sinking 51uA. That's not a really tough requirement, but if the layout was quite bad there could be 20 or 30mV along a trace. The TI part is a much higher current (and 50x more expensive) device, but it would typically be used in something with multilayer boards.

- 376,485

- 21

- 320

- 842

The terminology could be seen as ambiguous in some contexts. When encountered in an electrical design context Low/High, is usually a reference to the physical state of a binary digital signal, but on occasion it could imply a logical state as well.

Taking your example, many ICs provide an enable function, allowing the system to disable or enable the component explicitly. Traditionally these use a negative logic.

The following terminology may be more clear.

The system must assert the enable signal to turn on the device. The default state could be either asserted or deasserted depending on the IC and other components of the system, like Pull-Up resistors.

To provide this feature the IC implements a physical logic. Typically, this is defined by effectively standard CMOS or TTL thresholds, but it will definitely be spelled out in the datasheet.

If the IC implements a negative logic, this means that a voltage below the appropriate threshold must be present on the pin to assert the signal.

If the current voltage level is not correct or it is ambiguous/floating/UB then the system just effect a change on the voltage in order to turn the IC on using the enable feature.

In this case, we say that the system must drive the pin to the low voltage level in order to assert the signal and enable the device. The term stems from the typical realization of this which involves a transistor based amplifier, borrowing a term from analog electronics (to drive a speaker with an amplifier).

This terminology could be ambiguous in a few additional scenarios.

(1) It often includes the scenario where we wish to explicitly overcome any default state set through passive elements like pullups or other built in IC mechanism, even if the current voltage level is sufficient to enable the IC

(2) Some electrical systems allow a type of three state logic in addition to the typical binary interface. Instead of a distinct voltage level, often this is a "soft" version of high or low (sometimes both) . This practice stems from the TTL tradition of open collector or cmos open drain outputs. So driving a signal may also be interpreted as in contrast to providing a weaker signal through a discrete component or, for example, a pull up or down GPIO setting with a microcontroller .

- 5,797

- 1

- 20

- 43

It usually means pulling up or pulling down the pins. This is done to avoid the pin from being in a 'floating state'. When that pin is not being used or not connected to anything, it might have arbitrary signal due to noise for example. So the pin has to be pulled high to Vcc by a pull up resistor or pulled low to ground. Atleast this is what I understand.

- 59

- 4

-

No; pulling and driving a pin are two different things. As you say, pulling involves connecting to Vcc or ground through a resistor. Driving involves (effectively) tying the signal to Vcc or ground, so a driven signal will override a pulled signal. – Steve Melnikoff Mar 13 '21 at 09:26

-

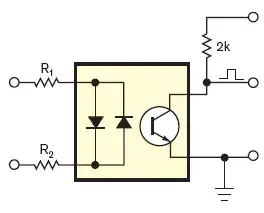

simulate this circuit – Schematic created using CircuitLab

Figure 1.

- (a) NOT1's input is driven low by SW2.

- (b) NOT2's input is driven hi by SW3.

- (c) NOT3's input can be driven high by turning Q1 on and Q2 off or driven low by turning Q1 off and Q2 on.

- (d) NOT4's input can be driven low by SW8 or "pulled" high by R1 when SW8 is opened.

In your case the chip ENABLE is configured as shown in Figure 1d. Pulling the input low will enable the chip. Technically that's really an inverted enable and should probably be labelled \$ \overline {ENABLE}\$ (NOT ENABLE) or \$ DISABLE \$. When you open SW8 an internal pull-up resistor will pull the voltage up to V+ and disable the chip.

- 168,990

- 12

- 186

- 385