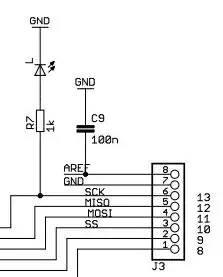

let's say I have an ADC with a full scale input from 0V to 2.1V. I want to protect the input of the ADC from voltages > 2.1V. I thought about using 3 diodes like shown below. Each diode has a breakdown voltage of 0.7V: When I use this circuit the ADC should be protected from voltages > 2.1V, right?

-

1Can you please provide a link to the datasheet for the ADC? Also, can you give a better description of the source of the signal (particularly its output impedance)? The maximum input voltage specification for the ADC may be different from the full-scale voltage. – Elliot Alderson Mar 07 '21 at 17:44

-

@ElliotAlderson their is no datasheet its more like a thought experiment. The signal would be coming from an op amp – Yoomo Mar 07 '21 at 17:47

-

5@Yoomo point is that no statement can't be made if you don't deliver specs for your signal source, and the source of things you want to protect against: for example, if the thing you want to protect against is ESD strong enough to jump the protections in the opamp, then it might also be strong enough to overload your diodes and kill your ADC. First and foremost, protecting against anything needs you to study what you're protecting against. Stating the voltage is not enough; you need to state the ability of the overvoltage source to supply current, otherwise all this is meaningless. – Marcus Müller Mar 07 '21 at 17:49

-

ADC should be protected agains voltages higher than ADC input is tolerant. It is usually the Vcc value (3v3, 5v). Btw, in your design if on the input is 2.1v, the signal will may be distored by diodes because diode at low currents start conducting at about 0.6v. Use zener diode rather. – Mar 07 '21 at 19:06

-

3Does this answer your question? [ADC protection best practice](https://electronics.stackexchange.com/questions/478413/adc-protection-best-practice) and [what-does-a-high-impedance-input-mean-for-an-adc](https://electronics.stackexchange.com/questions/501734/what-does-a-high-impedance-input-mean-for-an-adc/501737#501737). Mind the buffering. You probably want to buffer and protect the buffer. – DKNguyen Mar 07 '21 at 19:37

3 Answers

So let's take three real diodes, say the ubiquitous 1N4148 (or its also common SMT MELF version).

Now let's assume the ADC can tolerate 1K input resistance without unduly increasing error. Also let's assume the maximum input voltage is 25V. Doing a simulation:

It does limit the voltage typically to about 2.21V

Now let's see how it behaves with temperature at extremes -55/25/125°C At -55°C it limits it to 2.58V with 25V in and 1.76V at 125°C.

On top of temperature variations there will be some variation from unit-to-unit.

Now let's look at accuracy. Suppose we have a 12-bit ADC and we want the clamp to add no more than 1/2 LSB inaccuracy typically at +125°C.

Well that's not going to work. Even if we limit the full-scale voltage of the ADC to 500mV there is still 22mV of error or about 4.5% error.

Typically, at 25°C if the full scale voltage of the ADC is 1V we will add 0.4% of error. at 500mV about 250uV of error or about 2 bits worth on our 12-bit ADC.

So, it sort of works, but not very well, very consistently or very well over component variations and temperature. Low voltage zeners are horrible as well.

One simple approach in non-critical situations is to use a rail-to-rail op-amp buffer powered from the same rails as the ADC, and add series resistor allowing the op-amp protection networks to handle overvoltages (op-amps are usually more tolerant of series resistance than ADCs) . You can't expect good performance very close to the rails but other than that it works. One solution to the "close to the rails" issue is to supply the op-amp from slightly wider frails than the ADC, for example 5.25V and -0.25V rather than +5 and 0V.

An somewhat expensive but very effective solution is to use an op-amp or PGA that has the limiting function built-in.

- 376,485

- 21

- 320

- 842

CMOS devices already have ESD protection with 10k Series R to bipolar diodes to each rail and two such sets cascaded. (tiny low pF diodes with 5mA limits)

To improve on this you must know your potential fault source impedance and current being a problem . E.g. connected of Vdc , EMI or ESD or lighting impulse. Current input to device input must not exceed device so adding a small R is suggested with low capacitance TVS diodes for some applications. Your mileage many vary with low frequency and be adequate and reasonable source impedance.

Usually Vcm must be protected as well with clamps to each rail.

- 1

- 3

- 54

- 182

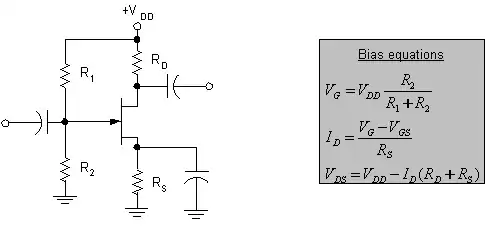

If it was a perfect diode, then yes it would work, however, the Vf of a diode at low currents isn't 0.6V so it will act as a clamp or current sink for the normal ADC voltage as well. Consider that what you are trying to do is limit a transition, then consider a resistor followed by a ESD or TVS diode and capacitor. (10 - 100n). The Resistor will limit the hit to the diode so as to limit the maximum current, the capacitor will help remove the high edge rate due to the RC time constant, and the diode will clamp any excess. (I read about this in an article a long time ago).

- 349

- 1

- 2