I'm building a full adder circuit using transistors. I am only doing it for fun, that's why I'm not using IC gates.

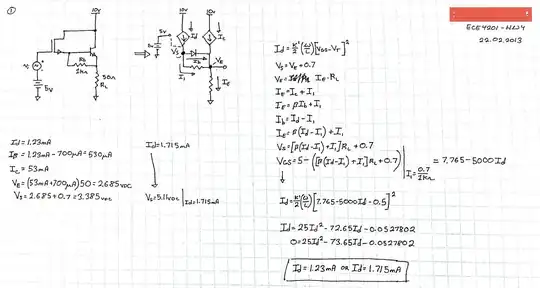

I am feeding it 5V and I'm getting really strange outputs. And it isn't even consistent, sometimes it does one thing and other times, other things. The outputs are around 3-4V, the LEDs sometimes shine normally, sometimes very faintly, sometimes not at all. And I just can't get it working. Can you see something off in my schematic?

And yes, I checked my PCB, I soldered everything good, there are no bridges.

I tried removing the resistors before the grounds, (R1, R6, R9, R18, R21, R26, R29, R32, R33) but it still doesn't work.