I strongly recommend adding an addendum at the bottom of your question that incorporates your comment that extends your question. You are now talking about multiplying a 4-bit binary input by 0x6. This requires at most a 7-bit result. (4 bits times 3 bits.)

Referring to the sidelined discussion I gave earlier (see below), multiplying by 6 just means that two of the partial products, \$PP_1\$ and \$PP_2\$, carry a meaningful value. The other two are just zero. And since you already know the constant is 6, these two partial products are just "lane changes" (shift left or shift right) for the bits. So there's no need for any AND logic, at all. So the partial product generator requires zero logic.

The only remaining thing is to sum up the two 4-bit partial terms aligned correctly with the output. A really simple modular approach is to use a half-adder for the lowest order computational output bit and full-adders for the rest.

Since the lowest order output bit is guaranteed to be '0', nothing is needed there. It's always '0'. The next lowest order output bit is just a copy of \$PP_1\$'s low-order bit. So no logic there, either. Just pass along the bit. The next lowest order bit has to perform a half-adder function. Etc.

If A is the 4-bit input then:

0 A3 A2 A1 A0 0

+ A3 A2 A1 A0 0 0

--------------------------

C2 S2 S2 S1 S0 A0 0

^ ^ ^ ^ ^

| | | | |

+<-HA<-FA<-FA<-HA

So you'll need two half-adders and two full-adders.

Do you think you can arrange that?

General Multiplier Approach

(What's below was my initial prodding answer. The OP has updated the question in comments so the following is no longer as directly relevant as it may have been before.)

I'll start you off. There are some "less obvious" methods. But, by and large, multiplier methods have a great deal of similarity with multi-digit multiplication techniques taught in grade school. You prepare partial products, shift them relative to each other, and then just add.

Suppose you arrange a schematic like this:

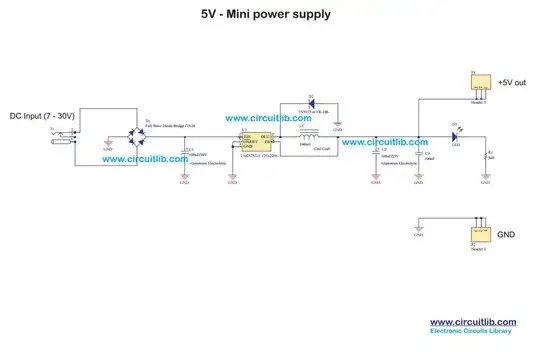

simulate this circuit – Schematic created using CircuitLab

In short, the A word enters from the left, the partial product term exits at right, and one of the bits from the B word determines whether the output is the A value or 0.

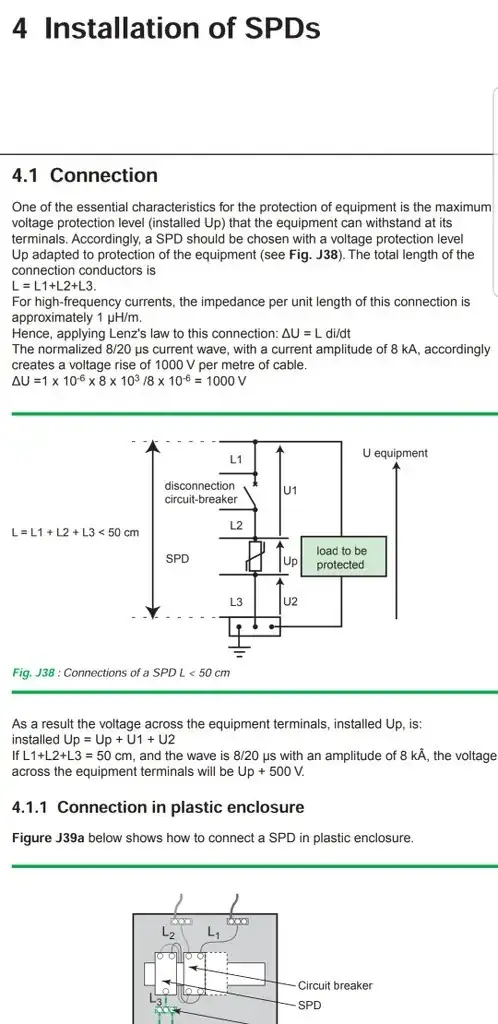

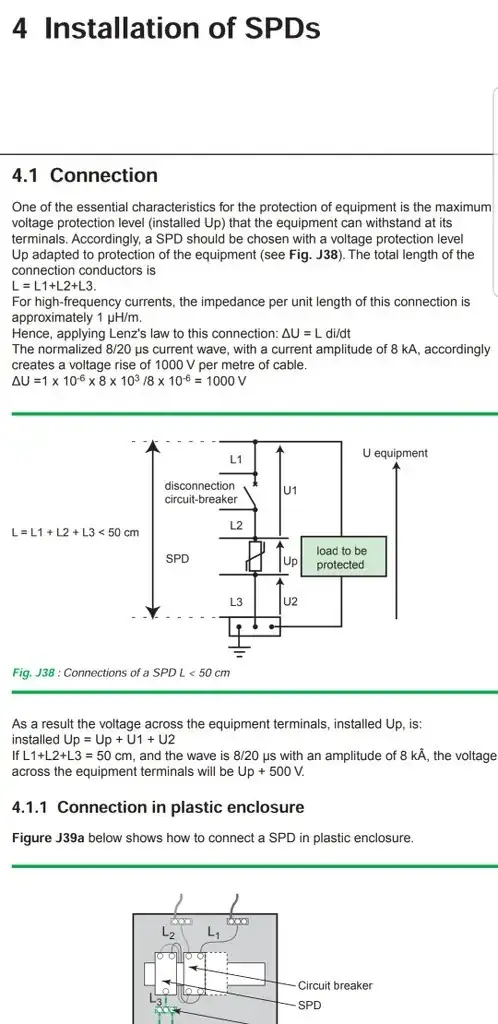

Now, you cobble up four of the above, such that:

simulate this circuit

That provides you with all four 4-bit partial products.

Now, at this point you can either add them up in the traditional way using half-adders and full-adders to get your final result or else, perhaps, you can study up on Wallace Trees, for example. Both will require 4 half-adders and 8 full-adders. But the Wallace Tree arrangement will have three fewer full-adder delays in the worst case path. So it's slightly better.

You can also review some more details found here.

I'll stop here, for now, and see how you respond. I may add more on the basis of what I see.