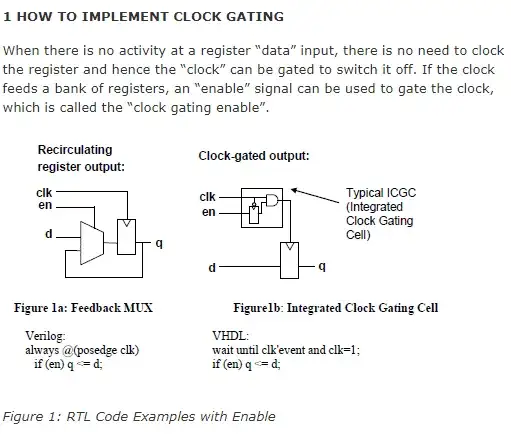

I'm studying to implement a Clock Gating in RTL. So I've followed as the below

https://www.design-reuse.com/articles/23701/power-analysis-clock-gating-rtl.html

always @(posedge clk)

begin

if (enable_in)

gclk <= clk;

end

But Problem is that I encounter an Error Message when I synthesis above code.

TOP.v:55: Clock clk used as data. (ELAB-305)

It does not makes sense Because this is just gating signal not a data. If I wrong, Could you please guide me?

How to implement Clock Gating STYLE code into RTL ?

Full Code :

module omsp_clock_gate (

// OUTPUTs

gclk, // Gated clock

// INPUTs

clk, // Clock

enable, // Clock enable

scan_enable // Scan enable (active during scan shifting)

);

// OUTPUTs

//=========

output reg gclk; // Gated clock

// INPUTs

//=========

input clk; // Clock

input enable; // Clock enable

input scan_enable; // Scan enable (active during scan shifting)

wire enable_in = (enable | scan_enable);

always @(posedge clk)

begin

if (enable_in)

gclk <= clk;

end

endmodule // omsp_clock_gate

module TOP(Clk, Reset, Crnt_Instrn, Zro_Flag, Carry_Flag, Neg_Flag, Return_Addr, Current_State, PC);

input Clk;

input Reset;

input [31:0] Crnt_Instrn; // Current Executing Inst

input Zro_Flag, Carry_Flag, Neg_Flag; // Flags from ALU or Stack

input [7:0] Return_Addr;

output [2:0] Current_State; // CurrentState from Control FSM

output [7:0] PC; // Program Count

wire Incrmnt_PC, Ld_Brnch_Addr, Ld_Rtn_Addr;

wire [2:0] CurrentState;

omsp_clock_gate u_omsp_clock_gate (

// OUTPUTs

.gclk ( gclk ), // Gated clock

// INPUTs

.clk ( Clk ), // Clock

.enable ( Neg_Flag ), // Clock enable

.scan_enable ( 1'b0) // Scan enable (active during scan shifting)

);

FSM I_FSM (

.Clk(Clk),

.Reset(Reset),

.CurrentState(CurrentState)

);

DECODE I_DECODE (

.Zro_Flag(Zro_Flag),

.Carry_Flag(Carry_Flag),

.Neg_Flag(Neg_Flag),

.CurrentState(CurrentState),

.Crnt_Instrn(Crnt_Instrn),

.Incrmnt_PC(Incrmnt_PC),

.Ld_Brnch_Addr(Ld_Brnch_Addr),

.Ld_Rtn_Addr(Ld_Rtn_Addr)

);

COUNT I_COUNT (

.Reset(Reset),

.Clk(Clk),

.Incrmnt_PC(Incrmnt_PC),

.Ld_Brnch_Addr(Ld_Brnch_Addr),

.Ld_Rtn_Addr(Ld_Rtn_Addr),

.Imm_Addr(Crnt_Instrn[7:0]),

.Return_Addr(Return_Addr),

.PC(PC)

);

assign Current_State = CurrentState;

endmodule