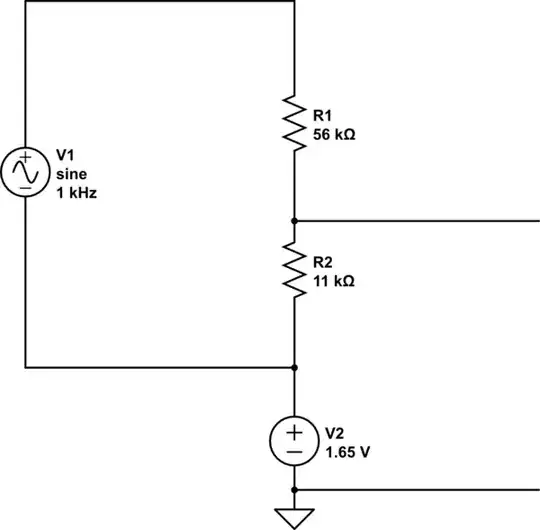

I've a question about the LTSpice simulation of the following simple LC circuit driven by a DC current source.

The first simulation (A) looks good from point of view of initial conditions for either voltage cap V(n001)=0 and inductor current I(L1)=0. As shown in the first picture the Initial Transient Solution (ITS) for the inductor current looks ok.

Consider now the second simulation (B) in which the initial condition has been set just for the inductor current I(L1)=0. This time, as shown in the second picture, that condition seems to be not honored (the initial inductor current results in 10A)

Can you help me in understanding the reason behind it ? Thanks

Edit: based on comments I've done another simulation (C) without any initial condition. As you can see the solver is able to work out the Initial Transient Solution (ITS) different from the previous two (A & B).

Can you point me to some book (or documentation) about how Spice works under the hood ? Thanks