I need a circuit/IC that can generate a single pulse with a variable pulse width (I would want a minimum of 50 ns but if that is not possible the next minimum can be 1 μs, and even if that is not possible then the final minimum can be 5 μs, depending on the achievable minimum, correspondingly the max can be 5 μs, 5 ms, 25 ms respectively) and variable amplitude with both positive and negative pulses in a range of ±5 V (practically the operation would be in ±2 V range) with a resolution of at least 10-20 mV. The variables need to be digitally controlled (preferably) but this is not a requirement. The current output can be a maximum of 2-3 mA. So I have searched a lot of the pulse generator ICs (monostable) available from different websites and companies (analog devices, data delay, maxim, etc) for 4 days now and I don't have anything that is the proper solution. All of them have variable pulse width and ± pulses which is good but the amplitude is the same as supply voltage and is not variable which is not good for me.

Here are the links to a few of the pulse generators I have searched for:

Data delay devices 3D3608 & 3D3612

The closest I have come to some potential solutions (might be wrong) are:

A. Pick any monostable multivibrator (such as LTC6993) and do either of the following for amplitude downscaling:

Use an 'AC voltage divider' or a 'Capacitor voltage divider' as mentioned in this answer. But I am not sure if this is the right way or if I should be careful about something such as drive current or capacitance of the pulse generator IC.

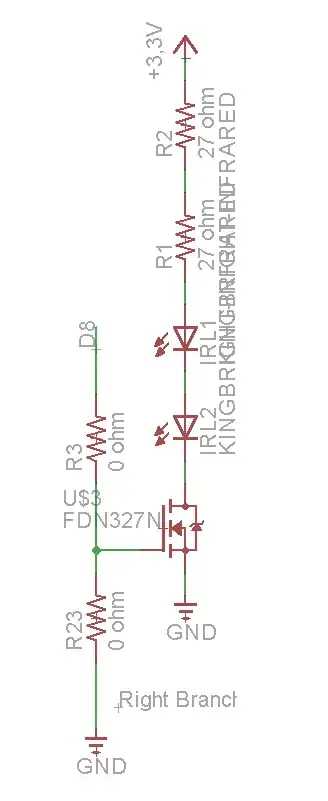

Use the output pulse (with an amplitude of 3.3 V / 5 V) of the monostable pulse generator to control the gate of a MOSFET with a lower drain-source voltage (typically 0.5-2 V) generated by a DAC.

B. Use a DAC to generate the (one-shot) pulse directly, I am not sure if it is possible to do this accurately (like a 1 μs pulse). If it possible, what kind of sampling rate/settling time/speed specifications I am looking for?

Thank you for reading everything. If you have a solution/advice (in form of a component, circuit, or a suggestion) please let me know, I would really appreciate it.