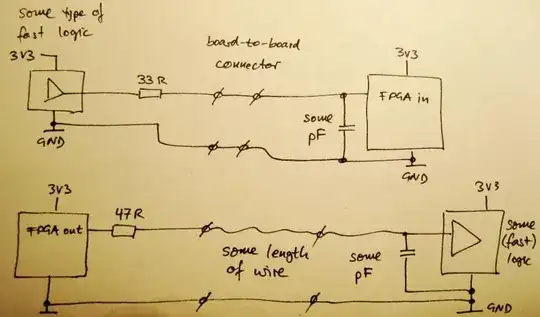

Is it good practice to slow down the slew rate of a CMOS output by putting an RC filter on it? What happens with impedance matching after I do this? Or can I just set the RC filter with such a low cut-off that transmission line effects don't need to be considered?

The CMOS output that is concerned here has a minimum 10-90% rise time of 1ns. Since I am running a trace that is around 250mm from this output, I want to minimize signal integrity issues.