I need to design a simple 4-way traffic controller for an assignment. Traffic is from Road 1, Road 2 and Road 3 (see diagram below). If there is traffic on road 1 only, road 1's traffic light stays green and the other roads stay red. Similarly for the other roads. If traffic on more than one road, then the green lights alternate.

The specifications say that I need to use a d-flip flop with asynchronous clear for the sequential circuit part.

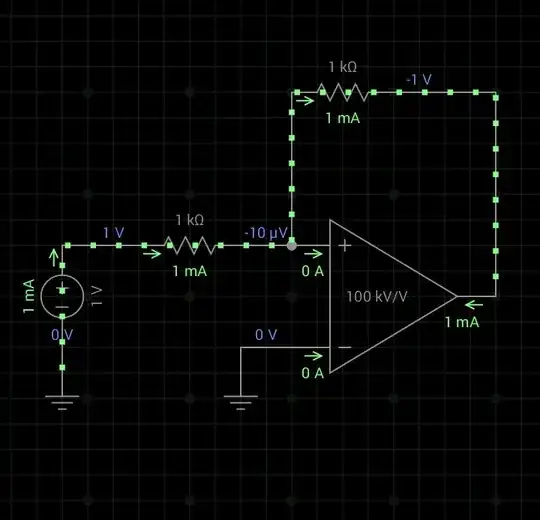

I have already designed the circuit. When using the built-in Logisim D flip-flop, the circuit operation is correct.

The assignment however requires us to implement the D flip-flop ourselves. I made a d flip flop as a subcircuit, and it seems to be working fine (outputs as expected)

However, when using my d flip flop in the main circuit, it works when only one of the inputs is asserted.

However, when using my d flip flop in the main circuit, it works when only one of the inputs is asserted.

If more than one input is 1, instead of alternating red and green lights, I get an "oscillation apparent"

The error definitely seems to be with my d flip flop implementation, and more specifically the asynchronous inputs, but I can't figure out what's wrong.

Let me know if I need to provide more information. Any help much appreciated, thank you!