Dithering is used to add virtual resolution to an oversampling ADC, and for instance this discussion involves some of the math involved, and the criteria.

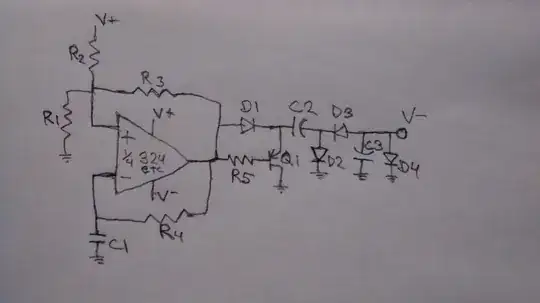

Take for instance an Arduino with 10 bit sampling. The unit has is the ability to set a digital pin to a random value, or a PWM output to a random value. It also has the ability to define a different Vref for ADC conversions. Would a simple circuit that drove the Vref with a filtered random digital signal between 5V and 1 LSB below 5V be a good solution for low-cost dithering?

The thought is that if the Vref were being altered, then the oversampling benefit would be available on all channels, not just one at a time. I can see there will be an over-read of the raw voltage of 0.5 LSB to be corrected for but this is a simple operation.

(I would add a schematic but the plugin seems to not work at present)