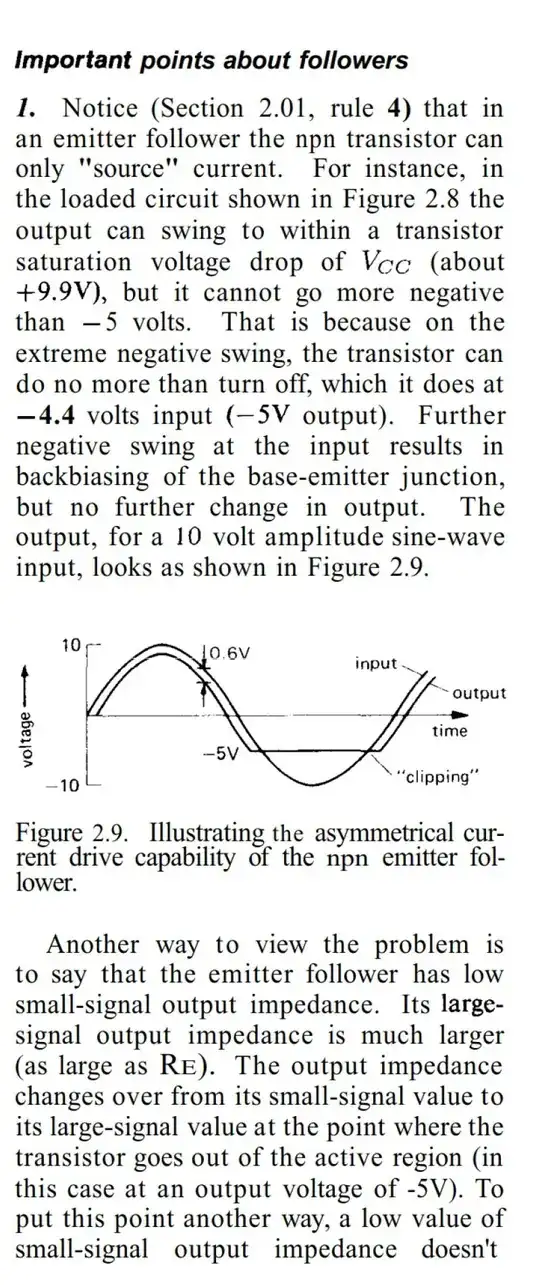

I have been rereading this section and realized I always get hung up here. The idea of clipping happening because the emitter is not able to stay .6 or so volts less positive than the base is familiar, but I find it difficult to be sure how that happens here.

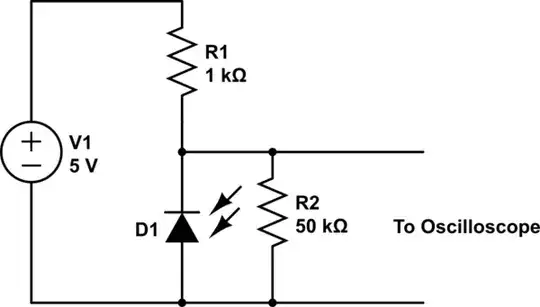

At positive input voltages of .6 volts or higher, it seems that positive current flows through the emitter resistor to the -10v supply and also through the load resistor to ground. Since the voltage drops are different, the currents through each resistor should be different, too. When the emitter reaches zero volts, the current through the load resistor crosses over to a negative flow, while the emitter resistor is still a positive flow. When the emitter reaches -5 volts, the forward drop across RE is exactly the same magnitude as the negative drop of RL, and beyond that point the transistor would need to be drawing current instead of supplying it, leading to cutoff because the emitter voltage will rise compared to the input at the base. Is this correct? I feel like I can't quite make the connection here.

I gather from internet searching that the distinction the authors make about large-signal vs. small-signal impedance has to do with the signal getting large enough (-5v in this case) to stop the linearity of the circuit, is that right? And is it the idea that the change in current direction at the load represents a change in the effective impedance?

When they say that the large-signal impedance is larger than the small-signal (as large as RE), do they mean that the load is somehow out of the circuit at that point, so we no longer enjoy the parallel resistance of both resistors? Edit: I guess that's the case, since up to -5v on the emitter the current is split (parallel) between RE and RL, but below that point all the current would have to go through RE (with the load current, [if there were any below this point] effectively passing through RL and RE in series?), right?

They also mention that the transistor can only source but not sink current. Is the idea here that if the base tries to draw current it does so without the aid of collector current? Or just that reversing the current direction immediately backbiases the BE junction? Any thoughts would be appreciated!

p.s. In the course of writing the question I think I might have figured out a big piece of the solution and the significance of the caption under the figure. Below the -5v point, RE is limited to (-5-(-10))v/1000= 5ma of current and falling, while the load resistor's current will be increasing above 5ma in the opposite direction. All the current drawn from the load then passes through RE. In order to reach -6V at the emitter, RE would have to draw -6ma through RL, but it can't because the voltage drop across RE is too small. So the base keeps getting more negative, but the emitter is stuck and thus the backbiasing. Right?

Sorry this is so wordy!