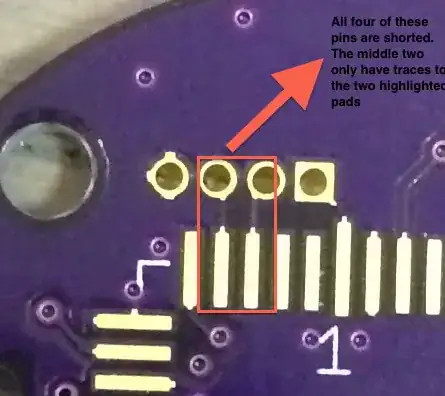

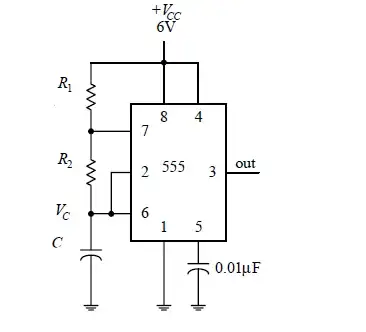

I have a question regarding the distortion I see at the transition of bit '0' and '1' in an FSK, I have the receiver connected to a sensing circuit at two frequencies, because my input is current limited at the sensing frequencies I would like the impedance to be as large as possible in order to get a good voltage range for sensing. I thought I might update the components with their respective parasitic resistance, because I am not sure whether the damping solely was the cause of it.

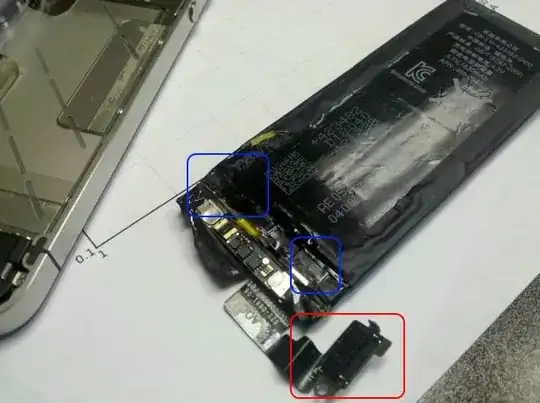

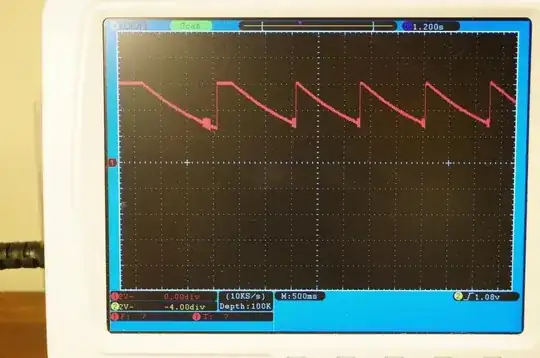

The response of the circuit looks something like this

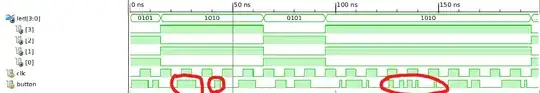

However, when I actually test the circuit together with the receiver, I see some distortions between transitions

and if I run an FFT this is the result I get, offsetting the window doesn't help either, so it's not because I am slicing into part of the previous bit.

I know the frequencies are all slightly different in these cases, it's because I had to tune my circuit a bit for 24 kHz and 32 kHz, but I don't think that would have changed the behaviour I observed so I hope the problem is still valid.

Basically, if I send a series of '010101010101....' and have a sliding window of baudrate (so say for example frequency 1 is 24 kHz, frequency 2 is 32 kHz and the baudrate is 4 kHz), instead of clearly seeing a tone at frequency 1 and frequency 2 for bit 0 and 1 for each bit, I essentially see a mix of two frequencies with similar amplitudes, and there is never a clean signal.

greatly appreciate any pointer!