From what i've understood from this article is that for a BJT in the

CE configuration, it provides minimal distortion at the output

No, CE configuration provides the most gain, but not minimal distortion. The article has a slightly misleading graph which shows that current amplification is linear, but voltage amplification is inherently non-linear due to the exponential relationship between Base voltage and current. In CE mode it is only linear for small signal excursions that don't change the Base voltage much.

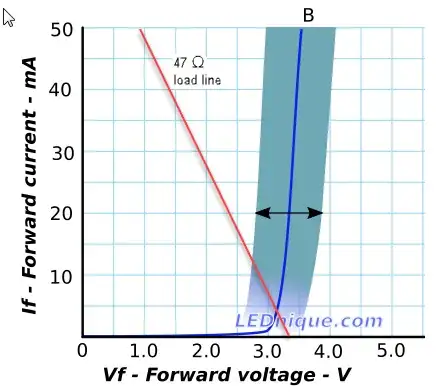

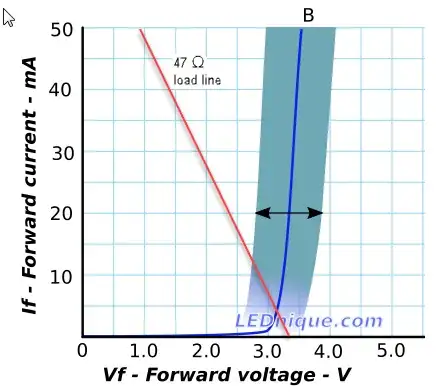

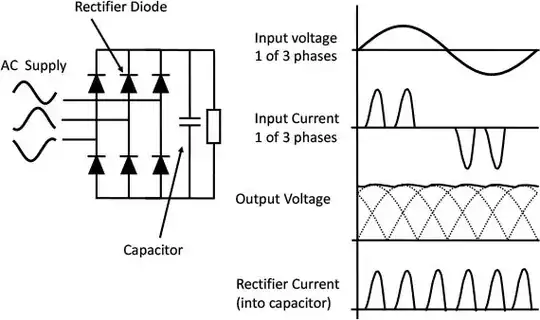

Here is a graph of typical Base voltage vs Collector current for the 2N3904. The curve may look linear, but only because the current axis is logarithmic.

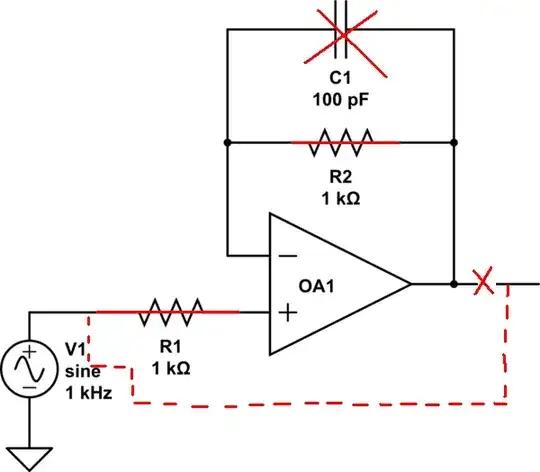

To improve linearity you can either apply negative feedback from output to input, add resistance in series with the Base to make current less sensitive to Base voltage, or apply Emitter degeneration by not fully bypassing the Emitter bias resistor. All these techniques trade gain for linearity.

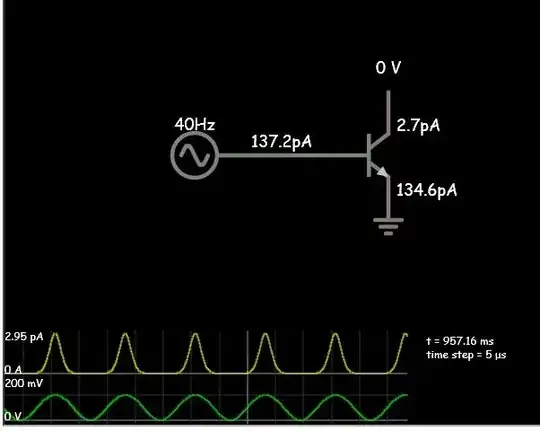

I did some simulations in LTspice to see what effect these techniques had on gain and distortion. I adjusted the sine wave input amplitude to get an output of 10 V peak to peak, and used FFT analysis to measure the amplitude of the 2nd harmonic (which is the major distortion product).

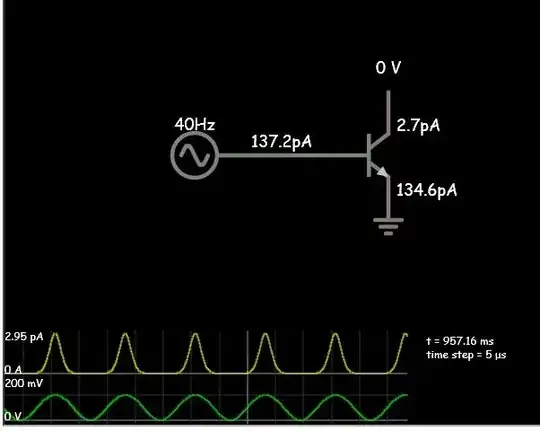

The first circuit I tried is the basic CE amp. It had excellent voltage gain of 46 dB, but the 2nd harmonic was only 16 dB down.

The output waveform was noticeably distorted due to the exponential rise in Base current as Base voltage increases, causing the output waveform to steepen as it goes down (Collector current increasing more).

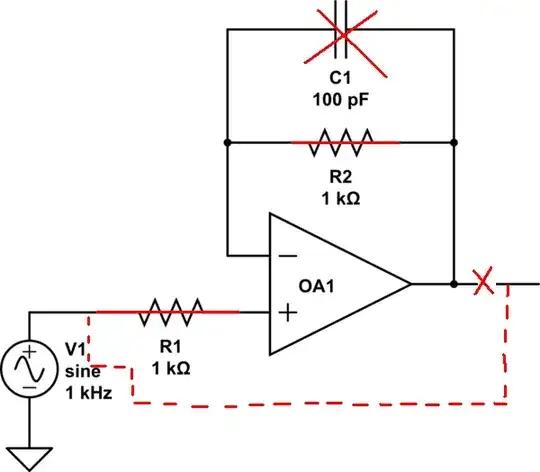

Next I moved the bias resistor to the output to help stabilize the DC operating point, and added a resistor at the input to linearize Base current and produce negative feedback (in conjunction with the bias resistor). This circuit had a reduced voltage gain of 28 dB, but the 2nd harmonic was 35 dB down. Much better!

Finally I tried a 4 resistor biasing scheme with Emitter degeneration. This has better DC stability, but maximum output voltage swing is reduced due to voltage drop across the Emitter resistor. It also had a voltage gain of 28 dB, but the 2nd harmonic was a bit more prominent at 32 dB down.