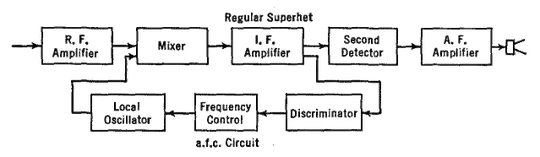

I'm using an ADC (ADS4129) running at 125MSPS. I'm applying a 100kHz sine wave to a low pass filter (fc=15MHz). The ADC is being driven differentially, as intended. When probing the input signal with a scope I see a decent sinusoid.

My problem is that looking at the ADC output I get this:

The frequency is right, but the points appear in clusters in specific points. At the moment I'm lacking several of the 10nF decoupling capacitors needed (I'm waiting for them). Could these capacitors be the cause of this problem? It seems strange to me that this appears at specific points.

On the other hand, analysing the input in the frequency domain seems to just indicate poor performance of the ADC, which would make sense without the decoupling needed.

Edit:

The ADC is in a Mezzanine board. I'm using a FPGA to interact with it. The FPGA is expecting a LVDS input signal, and it is converting the the data from the ADC format (DDR, alternating even and odd bits). This was tested in a testbench. The FPGA inputs were contrained according to the ADC setup and hold time, with a margin to account for possible trace length mismatch.

Edit 2:

transition:

0b111000011 451,

0b111111111 511,

0b111000001 449,

0b111111111 511,

0b111111101 509,

0b111111100 508