I am trying to see the behaviour of an NMOS' resistance with gate-source voltage.

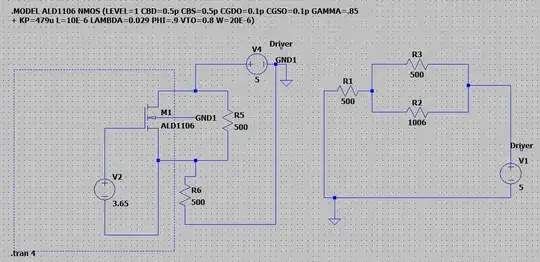

This is my NMOS as voltage (Vgs) controlled resistor' schematic (I am doing DC sweep on V2 from 2V to 10V with step size as 1V, ignore the -10V in the sweep in image):

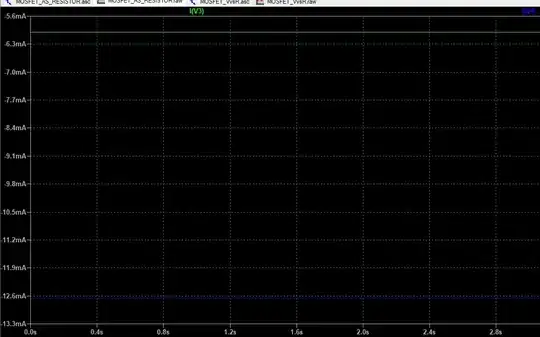

The output (Vgs or V2 vs NMOS resistance [Vds/I(R1)]) I get:

So at 3V Vgs, I get NMOS resistance of about 1 kilo ohms. I make a similar circuit on right by using a resistor with value of about 1 kilo omhs:

Points to observe:

- Vgs is set as 3V to get a resistance of 1001 ohms.

- The left and right circuits are similar, they only differ how the 1001 resistor is used. R6 is same as R4, R3 as R5 and so on.

- R5 is connected to ground and it shouldn't be, but then I could not make it connect in any other way because then it wouldn't make R5 parallel with the NMOS resistance as R3 is with R2

What is going unexpected: The current drawn/flowing the voltage sources V4 and V3 are not same. That means, the circuit on left is not doing a the job of a 1001 resistor. What went wrong? How should the left circuit be modified to emulate the 1001 ohm resistor on the right. I am feeling that I might have done something wrong with placing the V4 voltage source or maybe the NMOS resistance is somehow changing when other resistors are applied due to a new Vds (and not the same as the one in the first image).

However, I am not able to pinpoint the issue. So, how to make NMOS resistance behave like the normal resistor?

This is the ALD1106 LTSpice code:

.MODEL ALD1106 NMOS (LEVEL=1 CBD=0.5p CBS=0.5p CGDO=0.1p CGSO=0.1p GAMMA=.85

+ KP=479u L=10E-6 LAMBDA=0.029 PHI=.9 VTO=0.8 W=20E-6)