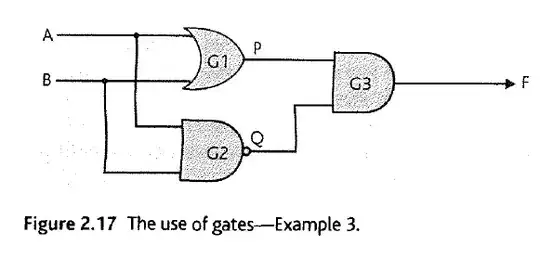

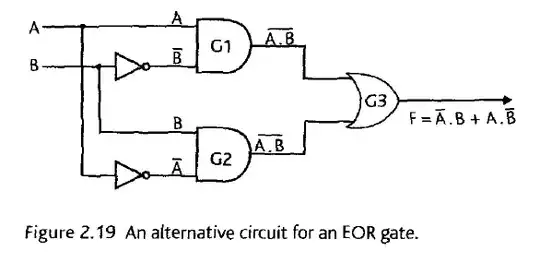

Both describe EOR(XOR) gate - but according to the textbook, it says that Figure 2.17 has two gates in series, while Figure 2.19 has three gates in series. But to my eye, it seems that both have three gates in series! Can anyone explain this? Thanks. Or is textbook's figure somehow wrong? (I heard that the textbook Principles of Computer Hardware has few figure errors in digital logic areas.