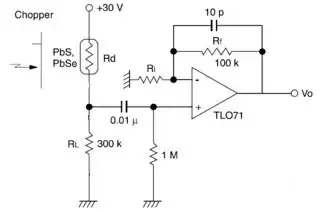

I have the following circuit:

I think I understand pretty much all the aspects of it except for the small capacitor in the feedback. What is the need for it? Judging by the frequency of 1 MHz that is the inverse product of the capacitance and the resistance, I can guess the need for this capacitor arises at high frequencies, when the gain of the amplifier tends to unity. However, I can't figure out the purpose.