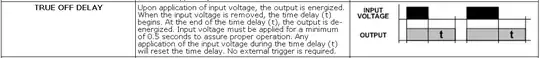

I am studying about rail-to-rail opamp design and I am trying to recreate the Itail vs Vgs (in this case input common voltage) curve from the link bellow (pages 5 and 6): https://mixsignal.files.wordpress.com/2013/03/689-604rail2rail.pdf

I am having trouble to recreate the plot for the PMOS input stage. My VDD and VSS voltages are 1.8 and -1.8, and bias current is 30uA and the passive load is enough to keep the PMOS in saturation. I have a feeling I am missing something basic with how I instantiated the current generator...

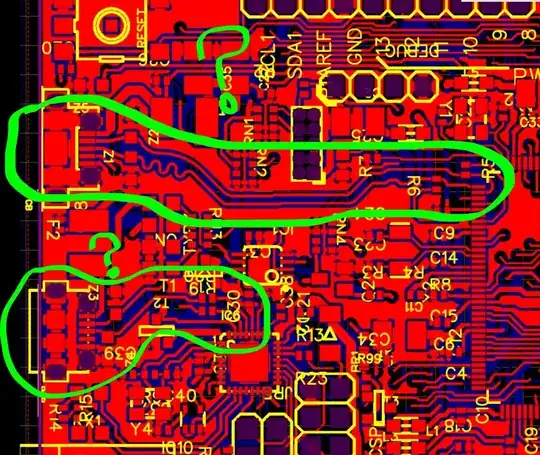

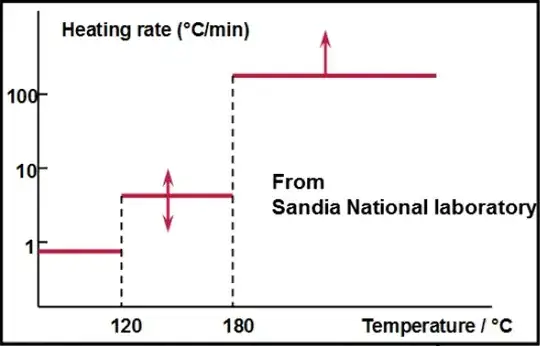

And here's my plot of the mosfet current vs input common voltage (you can see the drain current is a bit off, it looks as if I swept the Vds instead of gate voltage, and I didn't, I double checked):

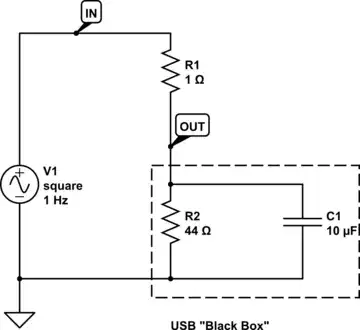

And finally, I tried putting it all together in one schematic cellview but again, I think I am using the bias generators wrongly because now I can't seem to see the correct current in the NMOS branches even thought there's the current generator...

I would appreciate some help. Thanks!

EDIT:

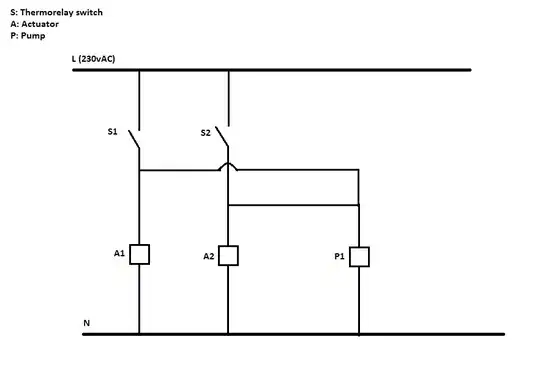

Taking a hint from the comments, I replaced the ideal current source with active current mirror source for both NMOS and PMOS differential input. I managed to get correct plots of drain current vs input common mode voltage and gm vs input common mode voltage but I still have troubles putting it all together into a rail-to-rail input stage (page 7 of the linked pdf).

The MOSFETs in the current mirrors are all the same, and what bothers me is that the NMOS M3 is not referencing the correct current from the current generator. My bias current is 40uA, and in individual cellviews where I simulated the PMOS/NMOS differential inputs separately everything worked fine.

Putting it all together now I seem to be having an issue with the PMOS branch again. You can see the simulation results in the next picture.

From the looks of it it seems my PMOS pair is always on and with fixed current through them.

EDIT2:::

After close inspection I realized my input common mode voltage generator was not properly grounded but connected to VSS (-1.8V). It kept my PMOS gate voltage always sufficient to drive them in saturation.

After correcting that mistake I was finally able to have my basic simulation set up and running.