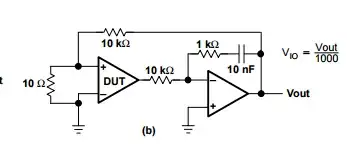

Spent a day trying to understand the maximum and minimum output voltage of the basic circuits as shown in this figure

The problem is that I have come across different expressions for the output voltage for these circuits. My analysis:

Comparing only the high side voltages, or maximum voltage swings in both cases

The circuit on the left: Common source configuration, supposed to have a "rail to rail" swing, which according to me means that the output voltage swings from vdd to ground. Some literatures disagree. Me too. The maximum output voltage for PMOS to remain in saturation is \$ Vdd-Vo>=Vsg - |Vtp| \$ and hence \$ Vo=<Vdd-Vsg + |Vtp| \$. This is not rail to rail. Solving it further, \$ Vo=<Vdd-(Vdd-Vi) + |Vtp| \$ and hence \$ Vo=<Vi + |Vtp| \$. What does this even mean?

The circuit on the right: Source follower configuration, gain is one. The maximum output voltage for NMOS to remain in saturation is \$ Vdd-Vo>=Vgs - Vtn \$ and hence \$ Vo=<Vdd-Vgs+Vtn \$. The same expression as above!!

What am I doing wrong here?

EDIT: The circuit to the left, if Vo is rail to rail then the PMOS will enter triode region and current sourcing ability will drop drastically, so again how is it rail to rail!