We use one n-type and one p-type MOS transistor for a NOT gate or one transistor and one resistor. Why can't we use one transistor only without a resistor?

-

4It's not clear what you're proposing. Can you draw a schematic, and clearly mark where your in- and outputs are? – Marcus Müller Sep 16 '20 at 06:01

-

6one transistor is only able to pull the output high or low, not both. – Light Sep 16 '20 at 06:08

-

the resistor is used as a separation point, after which the voltage is inverted, otherwise it would short the supply. in short, you _can_ use just one transistor, but it's a complete waste of power. – dandavis Sep 16 '20 at 06:20

-

How would you build the circuit? Show the circuit. Then we will tell you why the circuit doesn't work. – user253751 Sep 16 '20 at 13:48

-

But why do you want to have only one transistor for a NOT gate? – Sanmveg saini Sep 17 '20 at 11:12

2 Answers

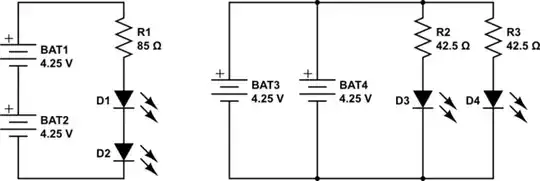

If you connect the collector of the transistor directly to the voltage, you will get a short circuit when the transistor opens. Even if the transistor stay alive after this without the resistor R2 you still have a logical 1 on the output because of a non-zero resistance of the open transistor.

- 2,150

- 11

- 29

Why can't we use one transistor only without a resistor?

Yes, it is possible... and it is used. The name of this configuration is "open drain". However, it has some limitations.

PMOS. If the load is grounded, we can control it only by a PMOSFET whose source is connected to Vdd (+5 V). Think of it as a switch that connects the load to Vdd when turned on. When turned off, the load is disconnected from Vdd (open circuit)... and if it has high resistance, it can be exposed to undesired voltages.

NMOS. If the load is connected to Vdd, we can control it only by an NMOSFET whose source is connected to ground. Think of it as a switch that connects the load to ground when turned on. When turned off, the load is disconnected from ground (open circuit) and if it has high resistance, it can be exposed to undesired voltages.

CMOS. The clever trick is to combine both configurations in one "complementary configuration". Then, when one of switches (transistors) is off, the other is on and the load is short circuited (firmly connected to the other rail). In this configuration, the load can be connected both to ground and Vdd.

So, the transistors connect the load either to Vdd or ground thus providing a path for the load current to exit Vdd or enter the ground. If we think of the ground as of another voltage source with zero voltage, we can say that two sources with voltages Vdd and 0 V are switched to the common load. Note that at a time only one of them is connected to the load.

RMOS. But it is interesting to see what the resistor does when connected between the drain and the supply rail (Vdd or ground). It acts as one of the switches (transistors) of the CMOS configuration above providing a continuous path for the load current. The resistor makes the "ideal" voltage source Vdd or 0 V (ground) with zero internal resistance behave as a real voltage source with Rd internal resistance... and this source is permanently connected to the load.

The trick here is that we do not disconnect the real voltage source (resistor) before to connect the "ideal" voltage source (transistor); we simply connect the "ideal" source in parallel to the real source without disconnecting it. Thus the "ideal" source overrides the real source and imposes its own voltage across the load.

- 13,593

- 1

- 17

- 48

-

1You can't create a normal open drain NOT gate because you can't connect the output of such gate to next gate without... the pull-up/down with a resistor! The hi-z can't go through the logic circuit. – Arseniy Sep 16 '20 at 13:26

-

We can call this device "an inverted open-drain output buffer". But the OP question is about a logic gate. – Arseniy Sep 16 '20 at 13:47

-