I'm using a STM32F746 running at 200MHz. A timer (tim2) is counting up at 100MHz and triggers an update interrupt with the following simplified ISR that writes a pattern to GPIOB

void __attribute__((section(".itcm_text"))) TIM2_IRQHandler(){

GPIOB->ODR=pattern[index];

index += 4;

if (index >= size)

index = 0;

htim2.Instance->SR &= ~0x1; //clear interrupt flag

}

To improve speed:

- ISR in ITCM

- Data in DTCM

- Interrupt priority is 0 ( no other interrupts at that level)

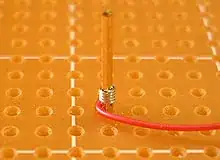

When triggering on the rising edge of a GPIO pin, there is visible jitter on the falling edge. The time step is exactly 5ns (one clock cycle) and 25ns total.

Question: Why? Can it be improved without using the timers capture/compare output mode?

Usually the interrupt latency is depending on flash memory timing, but this shouldn't involve the flash memory at all. Could it be AHB bus connection between CPU and GPIOB(also running at 200MHz)?