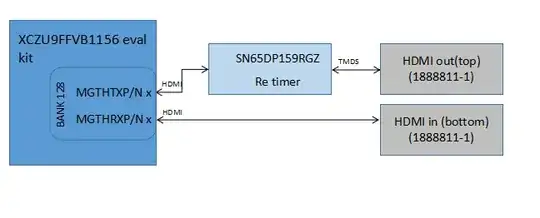

I am exploring a Zynq ultrascale+MPSoC design. While looking at the reference design of XCZU9FFVB1156 SOC evaluation board, in the HDMI interface there is a retimer IC in the transmitter side of Bank 128, which converts the HDMI signal to TMDS along and routed to HDMI output port. But in the receiver side, no such signal enhancing or TMDS to HDMI circuit is used.

I have attached the snapshot of my observation from the evaluation board design for reference.

Why is there no retimer or similar circuit in the HDMI input port? Please can you clarify the concept.