Logic buffer is usually depicted like this:

But can this work equally well?

And if it's not the case, why not?

Logic buffer is usually depicted like this:

But can this work equally well?

And if it's not the case, why not?

As a rule, the authors of circuit textbooks willingly show us how circuits are made... and how to calculate them. But they frequently forget to tell us why they are made this way; so usually we have to find the explanation ourselves.

It is a big challenge to reveal the "philosophy" behind these legendary complementary stages... to find the answer to the question, "Why are they made exactly this way?".. and to the more specific question here, "Why not a source follower?" I will try to do it in a human friendly manner, without any special terms and definitions that impede the intuitive understanding at this initial stage.

It really makes sense. He simply asks, "Why do we need to make a follower by two cascaded CMOS inverters (4 transistors in total) when such a simpler circuit (CMOS follower of only 2 transistors) exists?"

Really, it exists... and it is widely used in analog amplifiers... but here we are talking about digital circuits (logic gates). Let's consider what is the difference between them.

Following vs amplification. The output voltage of the CMOS follower is a copy of the input voltage. So, if the input signal has poor (sloping) transitions, the output signal will also be poor.

In contrast, the CMOS inverter has significant gain during the switching because each of the transistors acts as a "dynamic load" to the other. As a result, the input signal is amplified and its transitions become steep. So the CMOS inverter improves the input signal.

The fact that logic gates are amplifiers makes it possible to build latches by introducing a positive feedback (simply by connecting the output of the cascaded inverters to the input). It is impossible to make this by the source follower because its gain is less than one.

Output voltage drops. Analog circuits work in the middle range of the power supply (in active mode); their output voltage does not reach supply rails (ground and VDD). So, the voltage drops across the drain-source parts of both transistors can be significant... and they can be connected in a CMOS source follower configuration.

In contrast, digital circuits work close to supply rails; their output voltage is either 0 V (ground) or VDD (+5 V). This means that the voltage drops across the drain-source parts of both transistors should be almost zero... and they should be connected in a CMOS inverter configuration. So, the CMOS inverter provides voltage levels almost equal to the supply rails.

Input voltage thresholds. The voltage follower needs small voltage thresholds of the transistors since they determine the difference between the input and output voltage (i.e., here the voltage threshold is something undesired). That is why, BJT are more suitable for this configuration since their base-emitter voltage VBE (0.7 V) is a relatively small threshold.

In contrast, the complementary inverter needs significant voltage thresholds (but still < VDD/2) since both transistors switch close to middle (i.e., here the voltage threshold is desired). So, this topology can not be implemented by BJT because of their small thresholds. MOS FETs are more suitable for the inverting configuration because of their high gate-source voltage threshold Vth.

Biasing. Another problem of the follower is the absence of biasing. As a result, in a region of 2Vth, both transistors ate cut-off and the output is "floating". There is no such a problem in the invertor where at least one transistor is on.

Versatility. Cascaded inverters have another (great) advantage vs the follower - there is another input (output). It is used in RS latches and RAM cells.

No, your proposed buffer will not work well. MOSFETs are not ideal switches. For example, to make an NMOS conduct well you must bring its gate voltage significantly above the source voltage. In other words, when the transistor is conducting the source voltage must be significantly less than the gate voltage. In your buffer, if you bring the NMOS gate to Vdd the NMOS source (your output) will be significantly less than Vdd.

The "significantly less" value is determined by the threshold voltage of the transistors.

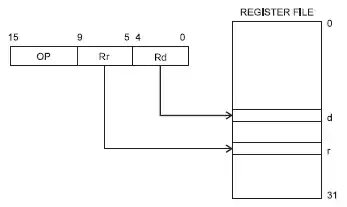

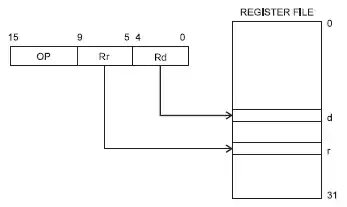

EECS 151/251A - Spring 2020 - Digital Design and Integrated Circuits - Lecture 9: CMOS

On the slide about transmission gates (#50), it is written that

Which I find a beautifully simple rule of thumb (I don’t know if it’s always correct though…)

The original schematic shows two cascaded CMOS inverters. The outputs are taken from the common-drain node.

In your schematic, the drain is tied to ground and the output is taken from the common-source node. As Elliot has detailed in his answer, your buffer gate will not work.

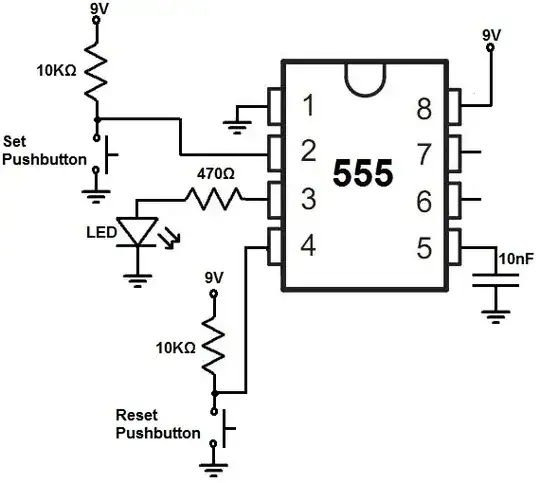

A two-transistor buffer is nothing different than a push-pull (a.k.a. totem pole) output:

simulate this circuit – Schematic created using CircuitLab

Maybe you should also ask another question like why two inverters instead of a single push-pull buffer?

FET diagrams like those shown for logic are a simplification. The bubble/no-bubble notation is shorthand for a p-FET or n-FET. It’s not really showing inversion per se, although that’s what the pair of FETs do when their sources are connected to VDD and Vss, as is usual for CMOS.

Looking deeper, a FET configured as a switch requires the right gate-source voltage to turn on properly:

For CMOS logic then, p-FETs are normally used on the pull-up side, while n-FETs are used in the pull-down.

On the other hand, the ‘flipped’ orientation doesn’t work. You won’t get the desired non-inverting behavior, as the gate-source biases are wrong.

Related: Why are the voltages the way they are in this transistor circuit?

Why do we use an inverter at the end in CMOS AND and OR gates?

Transmission gate logic bends this source-to-VDD/Vss rule some, but nonetheless still requires correct gate-source biases to pass a signal.