I was reading through the documentation of the AXI standard when I came across the interconnection matrix shown below. In short, the interconnection matrix provides a path for several masters to connect to several slaves at the same time. If there was only 1 master, then the interconnection matrix is basically a demultiplexer. However, with many masters, it is much more powerful. I was wondering how we can design such a thing in VHDL.

-

A quick Google search yields this Xilinx core datasheet https://www.xilinx.com/support/documentation/ip_documentation/axi_interconnect/v2_1/pg059-axi-interconnect.pdf which describes some typical use cases and architectures to support them. – Mr. Snrub Aug 03 '20 at 06:01

1 Answers

The AXI Interconnect Matrix is an example of a cross point switch, also known as a crossbar (pg 11 of the AXI IP documentation explicitly calls it that).

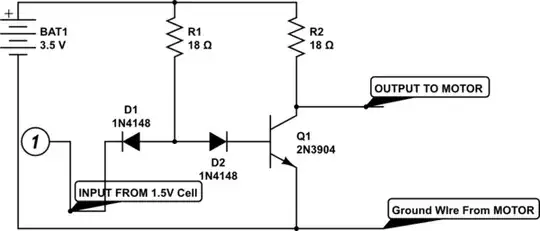

Below is a block diagram of a simple one I designed for a project I am working on:

In this example we have two entities that can read/write from one of 3 blocks of RAM. From L-R, the inputs (arbitrarily chosen as data and control signals can flow either way) are fed to 2 demuxes while they outputs are fed by 3 muxes. Control of what connections are actually used is governed by a separate Control Logic block.

The actual VHDL for this is rather simple. You just need to design a a Mux (if or case statement), a Demux (same as mux) and some control logic. By using generate statements to select the number of muxes/demuxes required you make a quite elegant structure that is fantastically scaleable.

- 878

- 5

- 10

-

-

#quantum231 Been a while since I posted my answer. What about fmax? The original question didn’t ask about that. However, if I intuit what you are asking correctly, different implementations will have different fmax. If you’d like to explore further, please ask another question! – Vance Aug 20 '21 at 22:07

-

I am using Xilinx tools now. The size of the interconnect goes into 10,000+ logic and easily becomes the biggest part of the entire design area-wise. A fully AXI4 compliant interconnect is just a very massive design block. Too large and too complex. – gyuunyuu Jun 22 '22 at 09:38