Working with:

- Lattice XP2-30 or XP2-40

- Tentatively a BGA484; almost certainly some BGA 1mm-pitch package

- Synplify PRO, with SystemVerilog

Skill level: Beginner / early-intermediate.

If I have a custom design (that is, to be implemented in a custom-made board) where there are several outputs for which timing must be matched to within, say, ±1ns (or whatever specified amount, perhaps less than 1ns), how can I ensure that these constraints are met?

Because I'm designing the board layout, I do not have the option to measure the skew, and then compensate for it by applying the opposite skew by adjusting the traces lengths. Not only that: I assume that any change in the HDL / re-synthesis / re-map / re-placement can potentially change the skew.

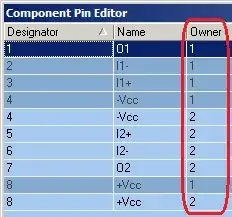

Another detail that constrains / complicates the problem: I would like to map the IO pins such that the layout gets easier to accomplish; for example, if I have the external chip (the one on the right in the image below) where I need to connect pins 1 to 5 with tight skew constraints, then that would strongly encourage the choice of FPGA pin assignments such that 1↔A16, 2↔B16, 3↔C16, 4↔D16, and 5↔E16 (just an example, assuming that A16 to E16 are IO pins), to have straight(ish) and near-equal-length traces and avoid using vias or having to "detour" some traces making a round behind the other one, etc.:

How can I ensure that the tool will be able (or will attempt) to implement things such that with that pin assignment, the timings and skew requirements can work?